Coprocessor Interface

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 11-17

ID012310 Non-Confidential, Unrestricted Access

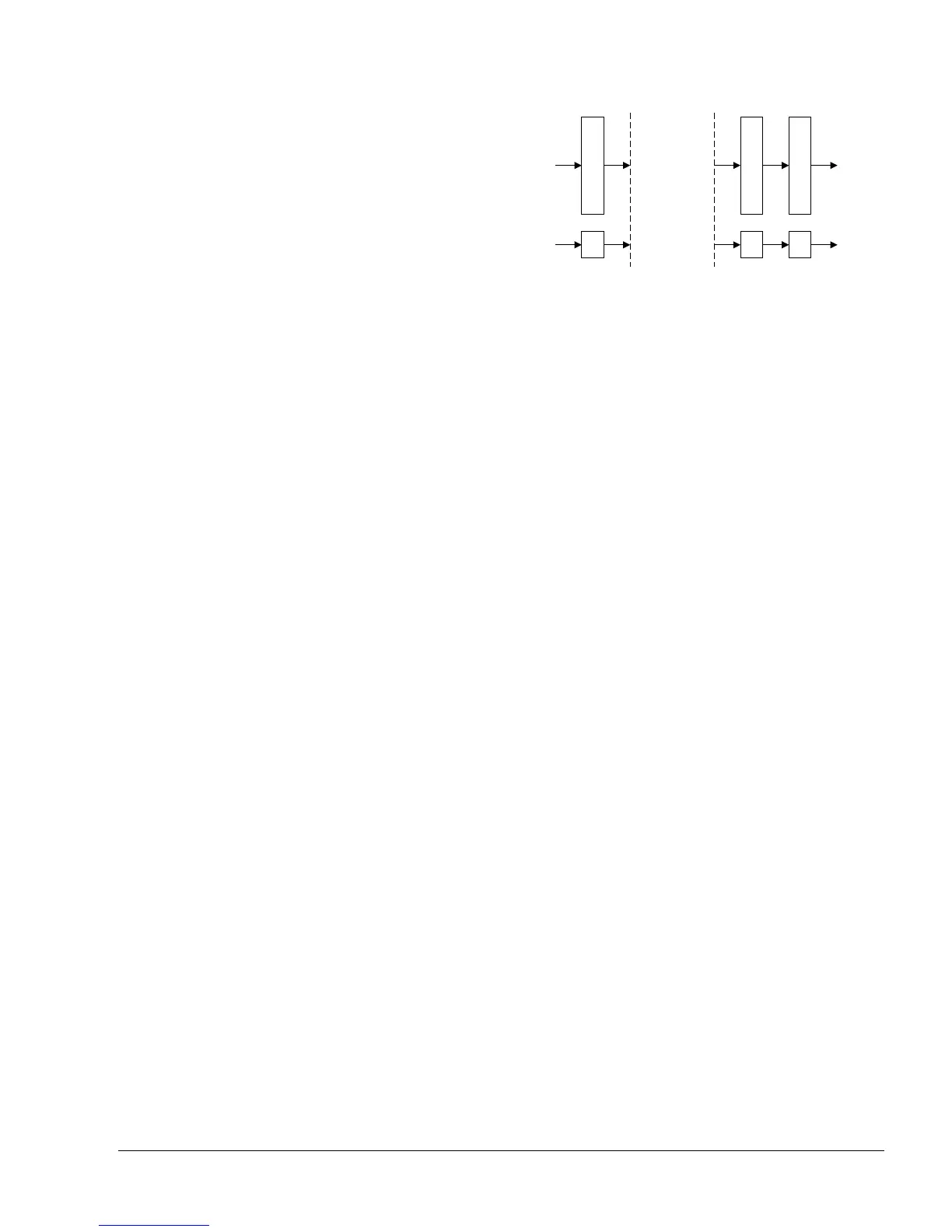

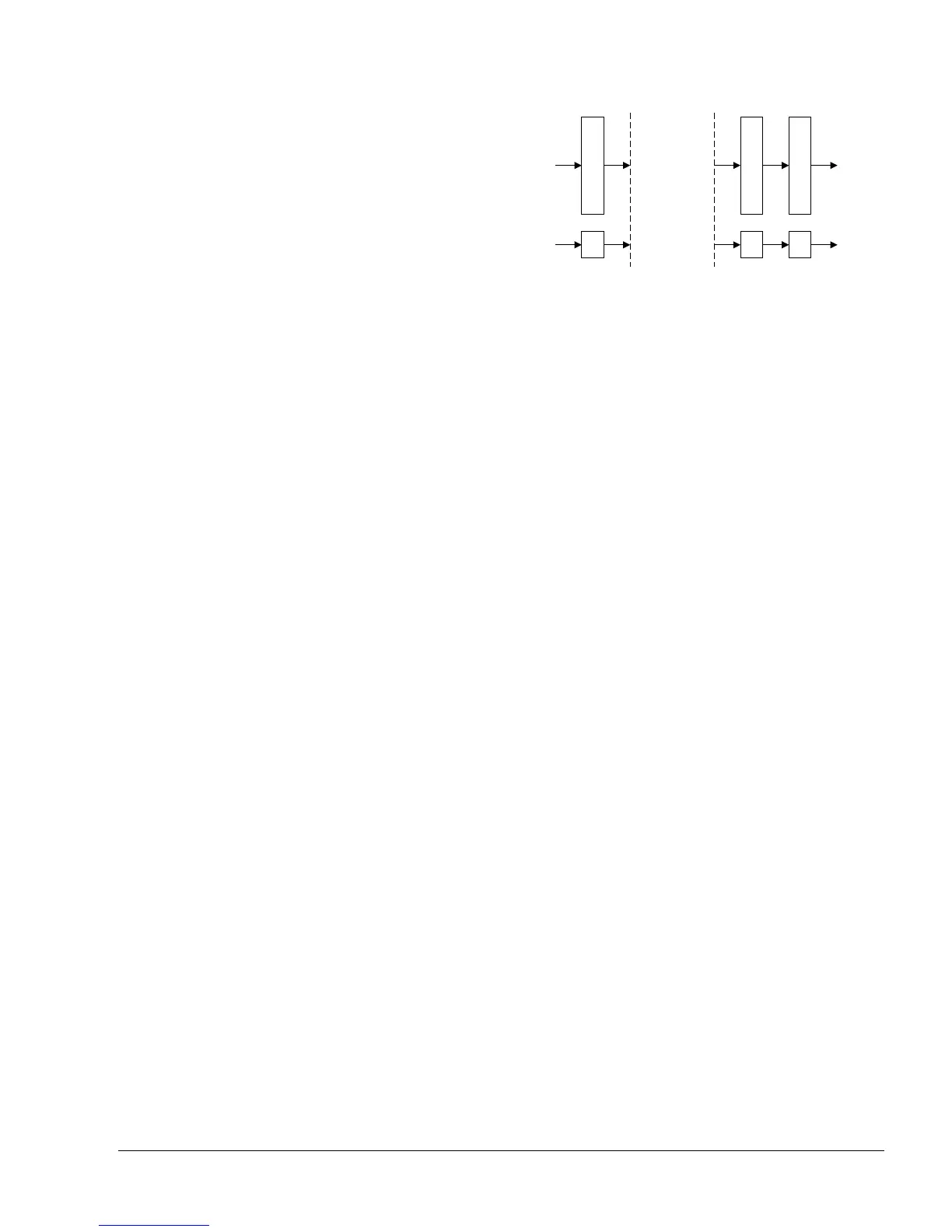

Figure 11-10 Load data buffering

The load data buffers function as pipeline registers and so require no flow control and are not

required to carry any tags. Only the data and a valid bit are required. For load transfers to work:

• instructions must always arrive in the coprocessor Ex6 stage coincident with, or before,

the arrival of the corresponding instruction in the core WBls stage

• finish tokens from the core must arrive at the same time as the corresponding load data

items arrive at the end of the load data pipeline buffers

• the LSU must see the token from the accept queue before it enables a load instruction to

move on from its Add stage.

Loads and flushes

If a flush does not involve the core WBls stage it cannot affect the load data buffers, and the load

transfer completes normally. If a flush is initiated by an instruction in the core WBls stage, this

is not a load instruction because load instructions cannot trigger a flush. Any coprocessor load

instructions behind the flush point find themselves stalled if they get as far as the Ex6 stage, for

the lack of a finish token, so no data transfers can have taken place. Any data in the load data

buffers expires naturally during the flush dead period while the pipeline reloads.

Loads and cancels

If a load instruction is canceled both the head and any tails must be removed. Because the

cancellation happens in the coprocessor Ex1 stage, no data transfers can have taken place and

therefore no special measures are required to deal with load data.

Loads and retirement

When a load instruction reaches the bottom of the coprocessor pipeline it must find a data item

at the end of the load data buffer. This applies to both head and tail instructions. Load

instructions do not use finish queue.

11.5.2 Stores

Store data emerge from the coprocessor issue stage and are received by the core LSU DC1 stage.

Each item of a vectored store is generated because the store instruction iterates in the

coprocessor issue stage. The iterated store instructions then pass down the pipeline but have no

other use, except to act as place markers for flushes and cancels.

Interconnect

InterconnectValid

Data

Valid

Data

WBls Ex6

Core Coprocessor

Loading...

Loading...