Debug

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 13-17

ID012310 Non-Confidential, Unrestricted Access

Table 13-9 lists the bit field definitions for context ID and non context ID Breakpoint Value

Registers.

When a context ID capable BRP is set for IMVA comparison, BVR bits [1:0] are ignored.

13.3.8 CP14 c80-c85, Breakpoint Control Registers (BCR)

These registers contain the necessary control bits for setting:

• breakpoints

• linked breakpoints.

Table 13-10 lists the Breakpoint Control Registers and that the processor implements.

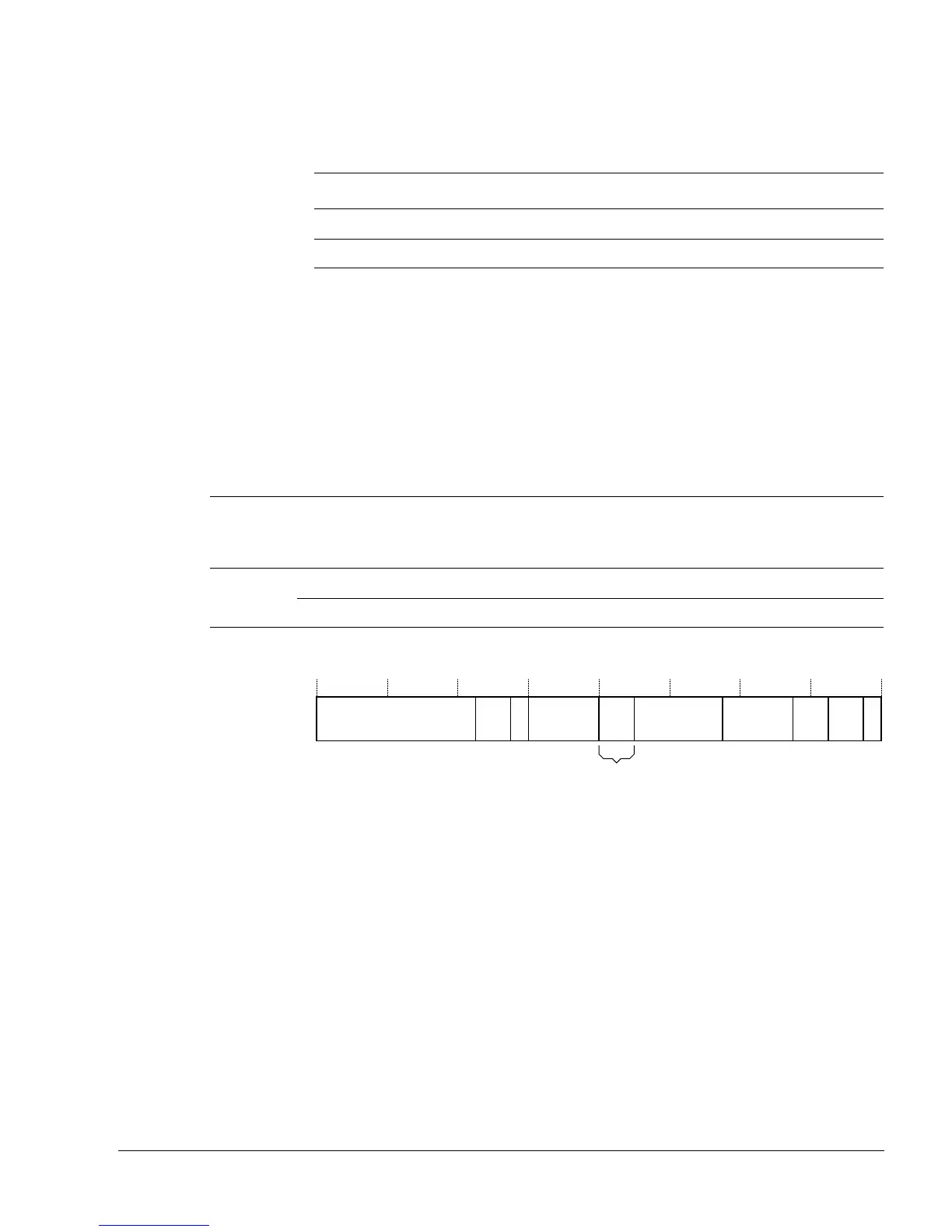

Figure 13-6 shows the format of the Breakpoint Control Registers.

Figure 13-6 Breakpoint Control Registers, format

Table 13-9 Breakpoint Value Registers, bit field definition

Context ID capable? Bits Read/write attributes Description

No [31:2] RW Breakpoint address

Yes [31:0] RW Breakpoint address or context ID

Table 13-10 Processor Breakpoint Control Registers

Binary address

Register

number

CP14 debug register name Abbreviation

Context ID

capable?

Opcode_2 CRm

b101 b0000-b0011 c80-c83 Breakpoint Control Registers 0-3 BCR0-3 No

b0100-b0101 c84-c85 Breakpoint Control Registers 4-5 BCR4-5 Yes

BUNP/SBZP

31

22

21

20 19 16 15 9 8 5 4 3 2 1 0

M E Linked BRP UNP/SBZP

Byte

address

select

UNP/

SBZ

S

23

1314

Secure breakpoint match

Loading...

Loading...