AC Characteristics

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 17-4

ID012310 Non-Confidential, Unrestricted Access

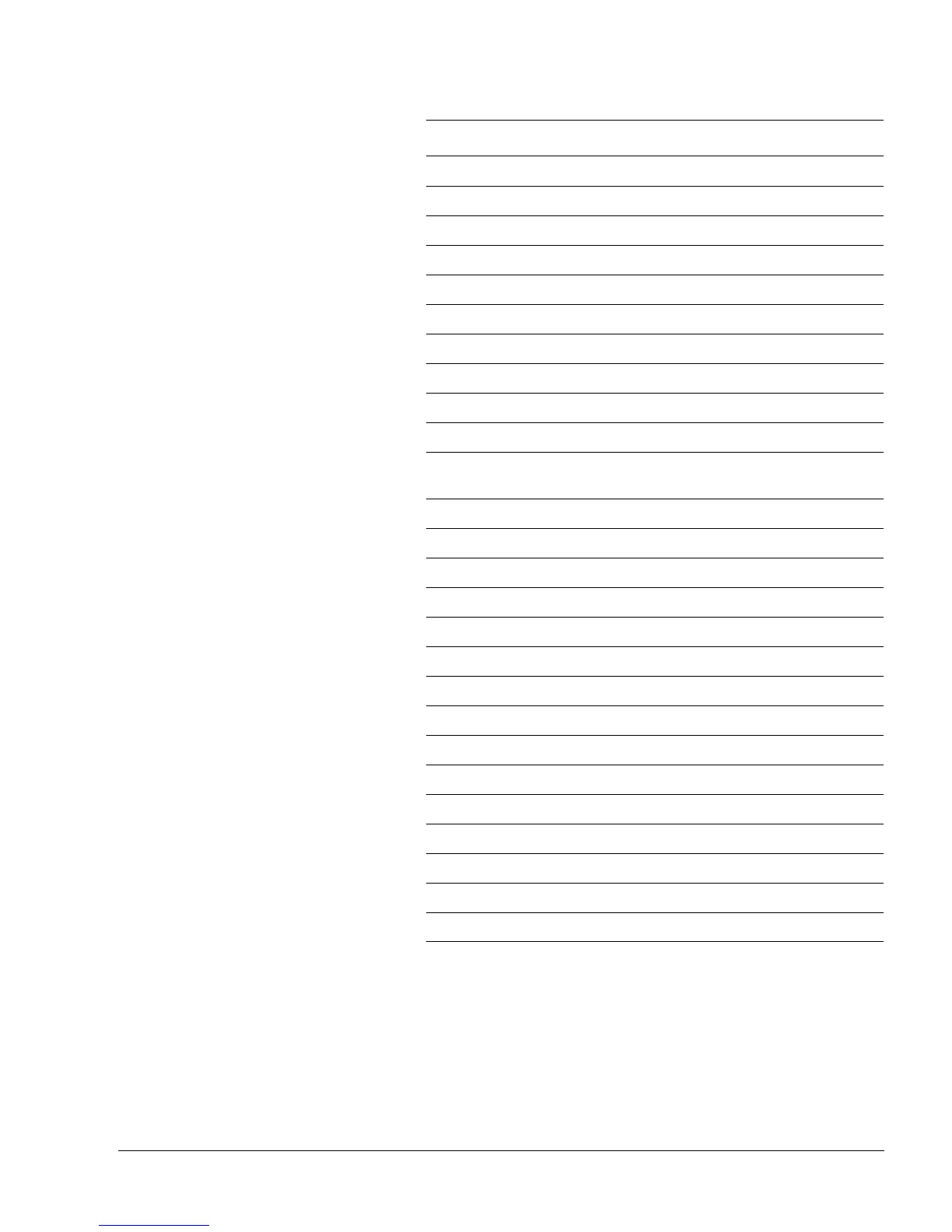

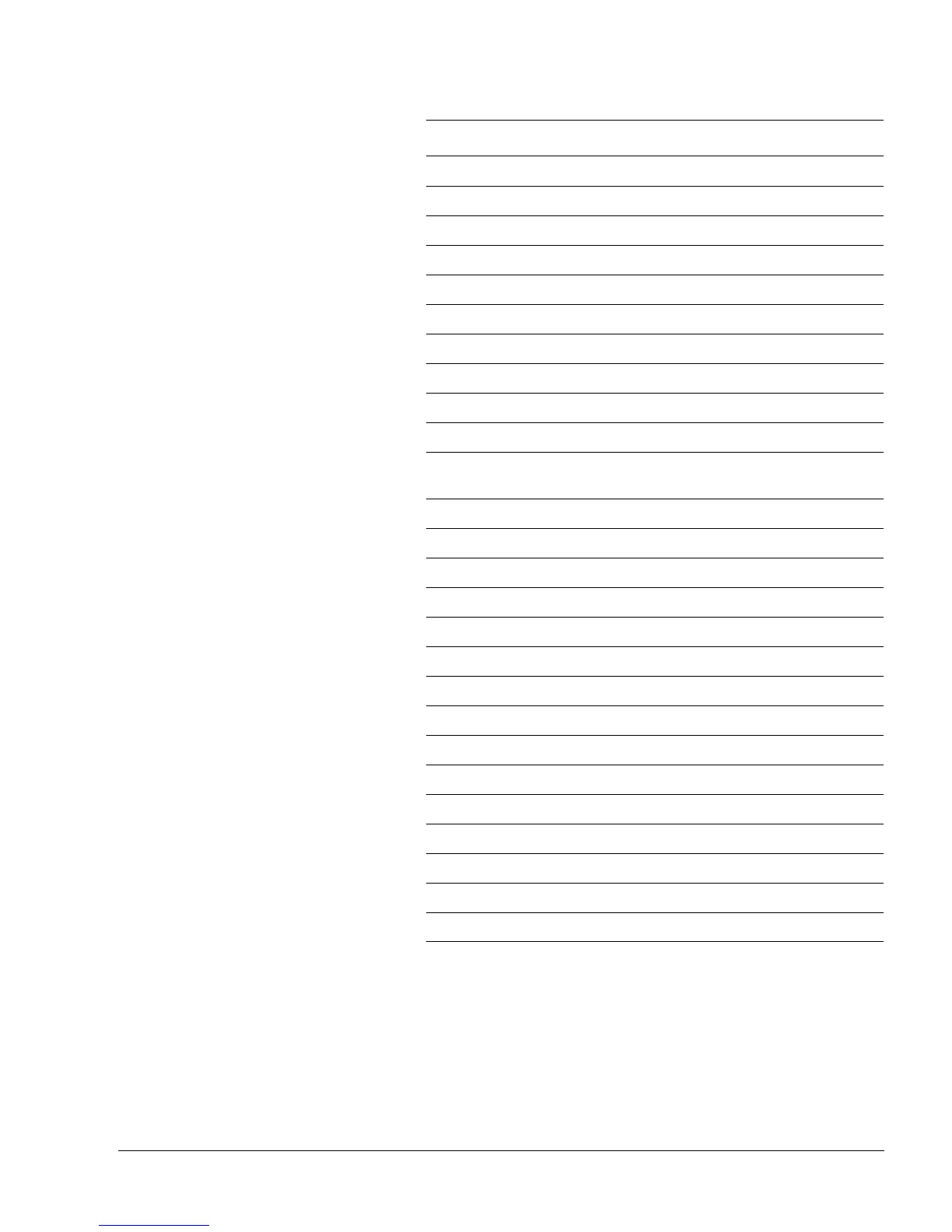

ARREADYRW Clock uncertainty 50

BRESPD[1:0] Clock uncertainty 70

BRESPP[1:0] Clock uncertainty 70

BRESPRW[1:0] Clock uncertainty 70

BVALIDD Clock uncertainty 50

BVALIDP Clock uncertainty 50

BVALIDRW Clock uncertainty 50

RDATAD[63:0] Clock uncertainty 70

RDATAI[63:0] Clock uncertainty 70

RDATAP[31:0] Clock uncertainty 70

RDATARW[63:0

]

Clock uncertainty 70

RLASTD Clock uncertainty 70

RLASTI Clock uncertainty 70

RLASTP Clock uncertainty 70

RLASTRW Clock uncertainty 70

RRESPD[1:0] Clock uncertainty 70

RRESPI[1:0] Clock uncertainty 70

RRESPP[1:0] Clock uncertainty 70

RRESPRW[1:0] Clock uncertainty 70

RVALIDD Clock uncertainty 50

RVALIDI Clock uncertainty 50

RVALIDP Clock uncertainty 50

RVALIDRW Clock uncertainty 50

WREADYD Clock uncertainty 50

WREADYP Clock uncertainty 50

WREADYRW Clock uncertainty 50

Table 17-2 AXI signals (continued)

Name Minimum input delay Maximum input delay%

Loading...

Loading...