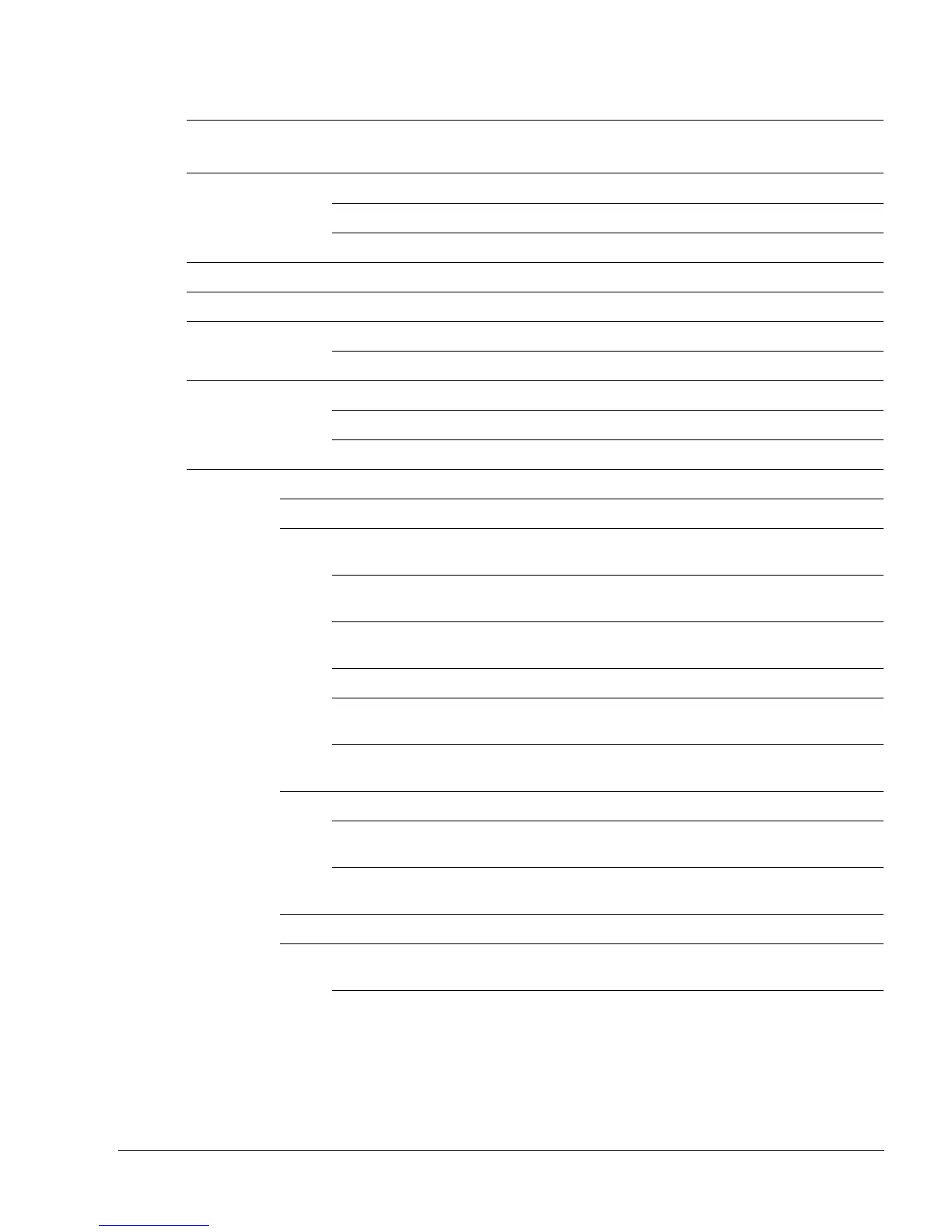

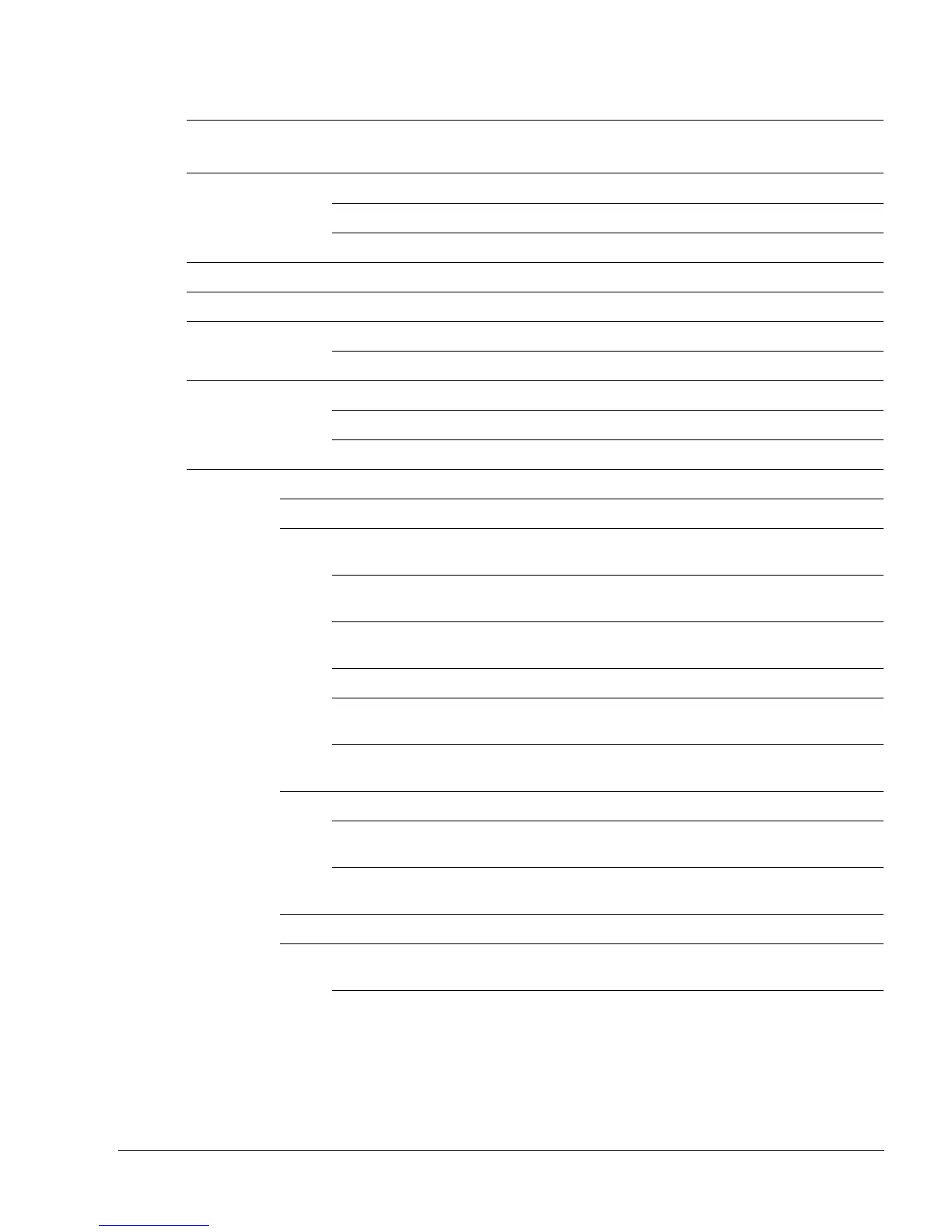

System Control Coprocessor

ARM DDI 0301H Copyright © 2004-2009 ARM Limited. All rights reserved. 3-15

ID012310 Non-Confidential, Unrestricted Access

c2 0 c0 0 Translation Table Base 0 R/W, B, X R/W

0x00000000

page 3-57

1 Translation Table Base 1 R/W, B R/W

0x00000000

page 3-59

2 Translation Table Base Control R/W, B, X R/W

0x00000000

page 3-60

c3 0 c0 0 Domain Access Control R/W, B, X R/W

0x00000000

page 3-63

c4 Not used

c5 0 c0 0 Data Fault Status R/W, B R/W

0x00000000

page 3-64

1 Instruction Fault Status R/W, B R/W

0x00000000

page 3-66

c6 0 c0 0 Fault Address R/W, B R/W

0x00000000

page 3-68

1 Watchpoint Fault Address R/W NA

0x00000000

page 3-69

2 Instruction Fault Address R/W, B R/W

0x00000000

page 3-69

c7 0 c0 4 Wait For Interrupt WO WO - page 3-85

c4 0 PA R/W, B R/W

0x00000000

page 3-80

c5 0 Invalidate Entire Instruction

Cache

WO WO, X - page 3-71

1 Invalidate Instruction Cache

Line by MVA

WO WO - page 3-71

2 Invalidate Instruction Cache

Line by Index

WO WO - page 3-71

4 Flush Prefetch Buffer WO WO -page3-79

6 Flush Entire Branch Target

Cache

WO WO - page 3-79

7 Flush Branch Target Cache

Entry by MVA

WO WO - page 3-79

c6 0 Invalidate Entire Data Cache WO NA - page 3-71

1 Invalidate Data Cache Line by

MVA

WO WO - page 3-71

2 Invalidate Data Cache Line by

Index

WO WO - page 3-71

c7 0 Invalidate Both Caches WO NA - page 3-71

c8 0-3 VA to PA translation in the

current world

WO WO - page 3-82

4-7 VA to PA translation in the

other world

WO NA - page 3-83

Table 3-2 Summary of CP15 registers and operations (continued)

CRn Op1 CRm Op2 Register or operation S type

NS

type

Reset

value

Page

Loading...

Loading...