MAX32665-MAX32668 User Guide

Maxim Integrated Page 106 of 457

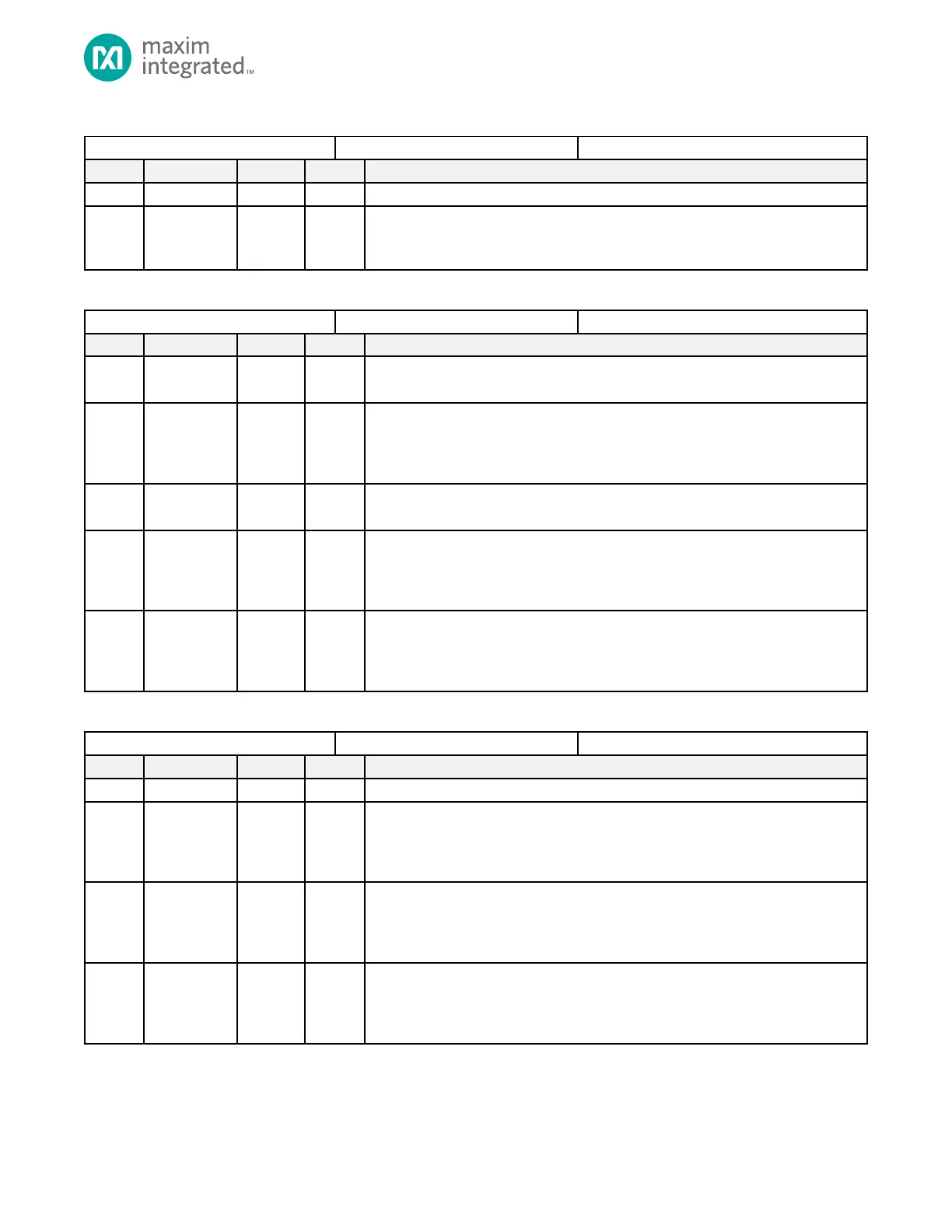

Table 4-66: Revision Register

Device Revision

Returns the chip revision ID as a packed BCD. For example, 0xA1 would indicate the

device is revision A1.

Table 4-67: System Status Interrupt Enable Register

System Status Interrupt Enable

Reserved

Do not modify this field.

SRCC Cache Memory Fault Interrupt Enable

Generates an interrupt if hardware detects an error in the SPIXR code.

0: Disabled.

1: Enabled.

Reserved

Do not modify this field.

SPIXF Code Integrity Error Interrupt Enable

Generates an interrupt if hardware detects an error in the SPIXF.

0: Disabled.

1: Enabled.

Arm ICE Unlocked Interrupt Enable

Generates an interrupt if the Arm ICE is unlocked.

0: Disabled.

1: Enabled.

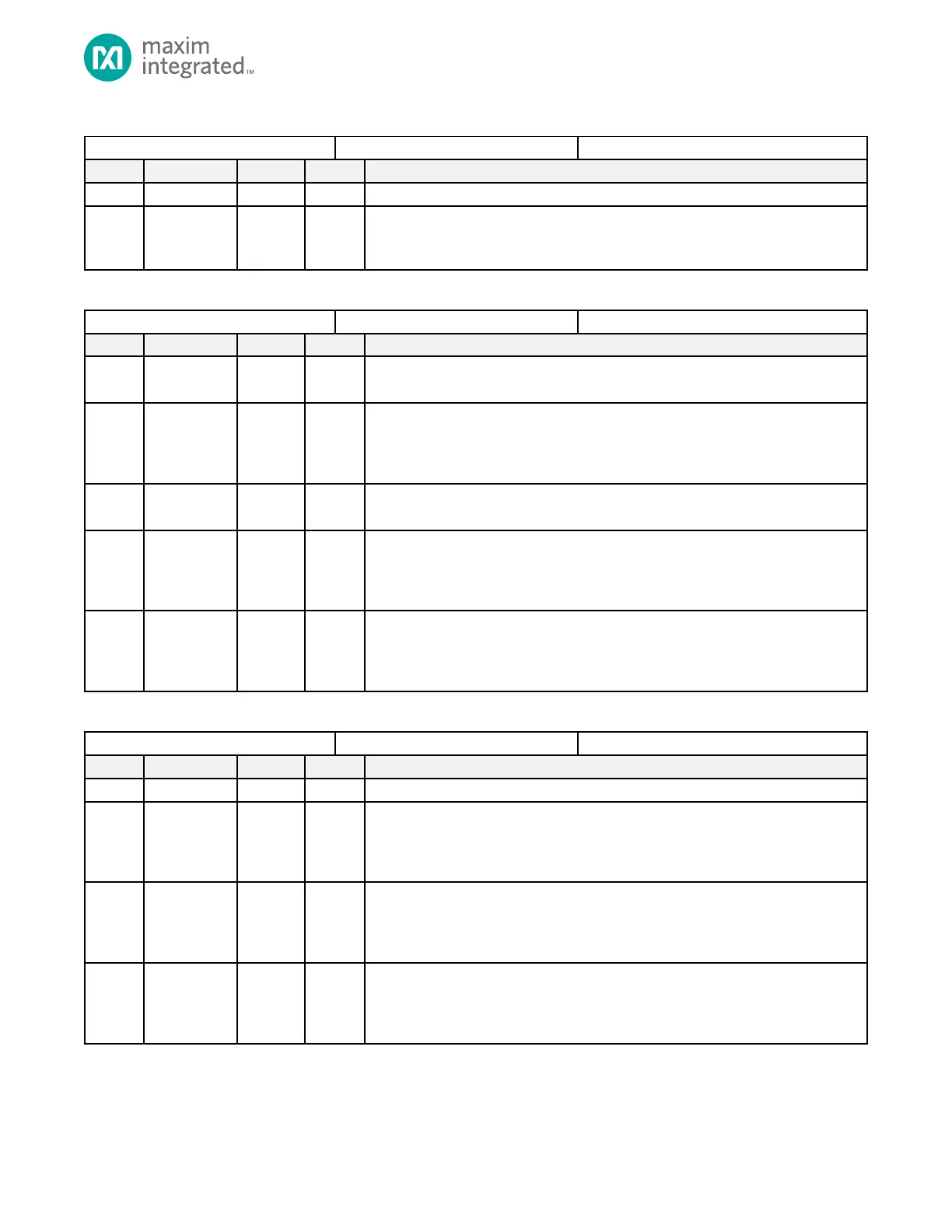

Table 4-68: Error Correction Coding Error Register

Error Correction Coding Error

Flash1 ECC Error

Write to 1 to clear the flag.

0: No error

1: Error

Flash0 ECC Error

Write to 1 to clear the flag.

0: No error

1: Error

SPIXF Instruction Cache ECC Error

Write to 1 to clear the flag.

0: No error

1: Error

Loading...

Loading...