MAX32665-MAX32668 User Guide

Maxim Integrated Page 98 of 457

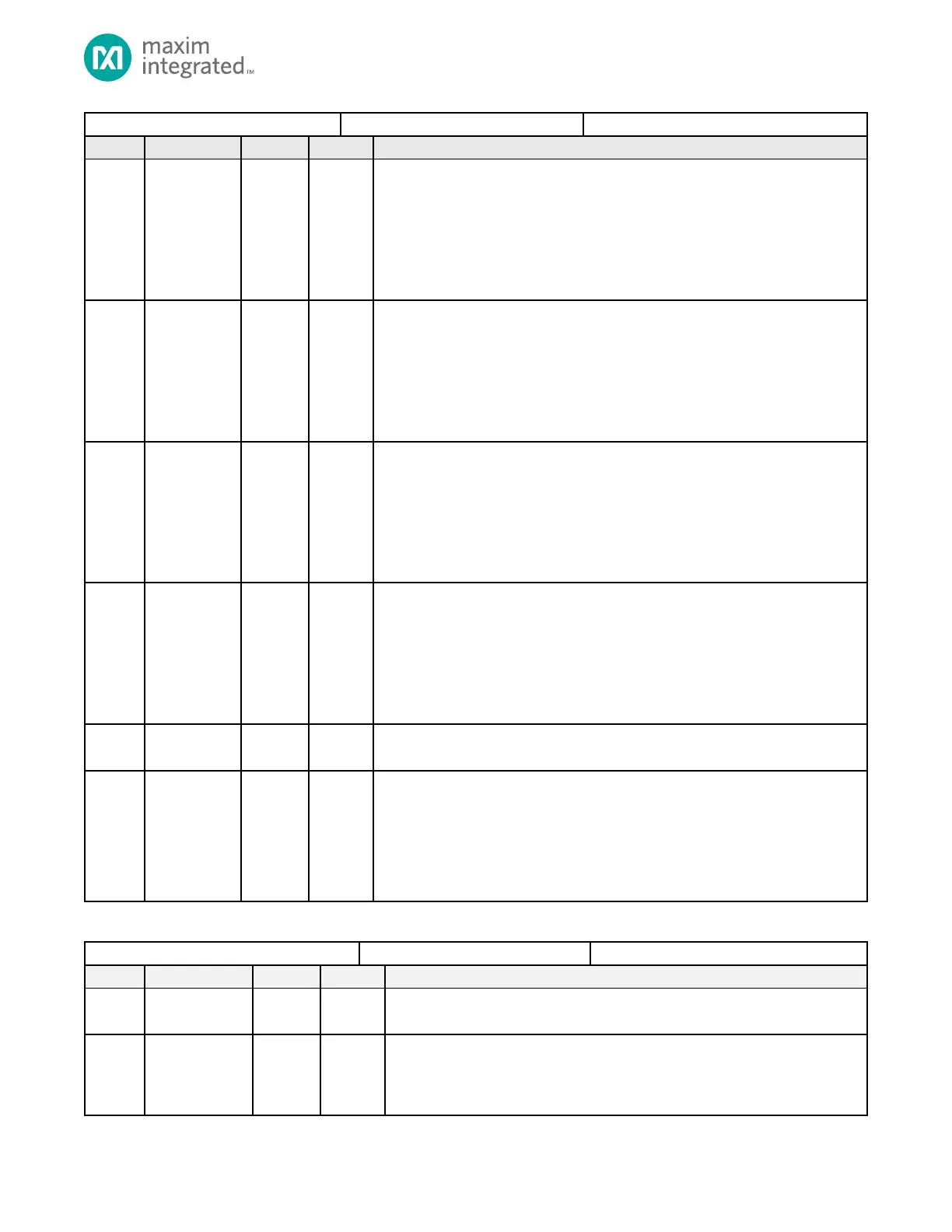

Sysram3 LIGHTSLEEP Enable

Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained.

See Table 4-13 RAM for base address and size information.

0: ACTIVE mode.

1: LIGHTSLEEP mode enabled.

Note: To put RAM in a shutdown mode that removes all power from the RAM and

reset the RAM contents, use the PWRSEQ_LPMEMSD register.

Sysram2 LIGHTSLEEP Enable

Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained.

See Table 4-13 RAM for base address and size information.

0: ACTIVE mode.

1: LIGHTSLEEP mode enabled.

Note: To put RAM in a shutdown mode that removes all power from the RAM and

reset the RAM contents, use the PWRSEQ_LPMEMSD register.

Sysram1 LIGHTSLEEP Enable

Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained.

See Table 4-13 RAM for base address and size information.

0: ACTIVE mode.

1: LIGHTSLEEP mode enabled.

Note: To put RAM in a shutdown mode that removes all power from the RAM and

reset the RAM contents, use the PWRSEQ_LPMEMSD register.

Sysram0 LIGHTSLEEP Enable

Data is unavailable for read/write operations in LIGHTSLEEP mode but is retained.

See Table 4-13 RAM for base address and size information.

0: ACTIVE mode.

1: LIGHTSLEEP mode enabled.

Note: To put RAM in a shutdown mode that removes all power from the RAM and

reset the RAM contents, use the PWRSEQ_LPMEMSD register.

Reserved

Do not modify this field.

Program Flash Wait States

Number of wait-state cycles per Flash code read access.

0: Invalid

1 – 7: Number of Flash code access wait states

Note: For the 60MHz clock and slower, minimum wait state is 1.

Note: For the 96MHz clock, the minimum wait states should be 2.

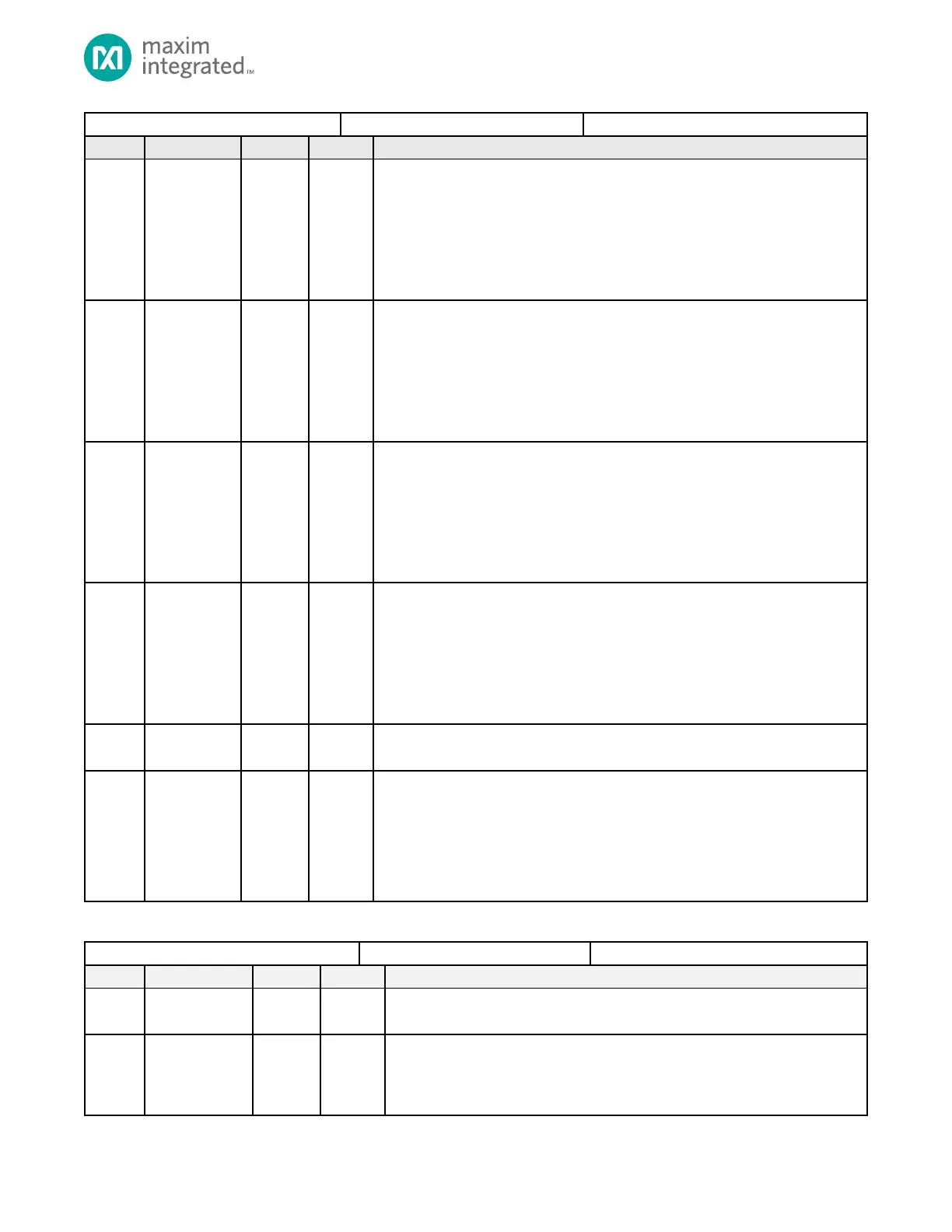

Table 4-61: Memory Zeroization Control Register

Memory Zeroization Control

Reserved

Do not modify this field.

CPU1 ICC1 Cache Data and Tag Zeroization

Write 1 to initiate the operation. Only valid on devices with optional CPU1.

0: Operation complete.

1: Operation in progress.

Loading...

Loading...