MAX32665-MAX32668 User Guide

Maxim Integrated Page 86 of 457

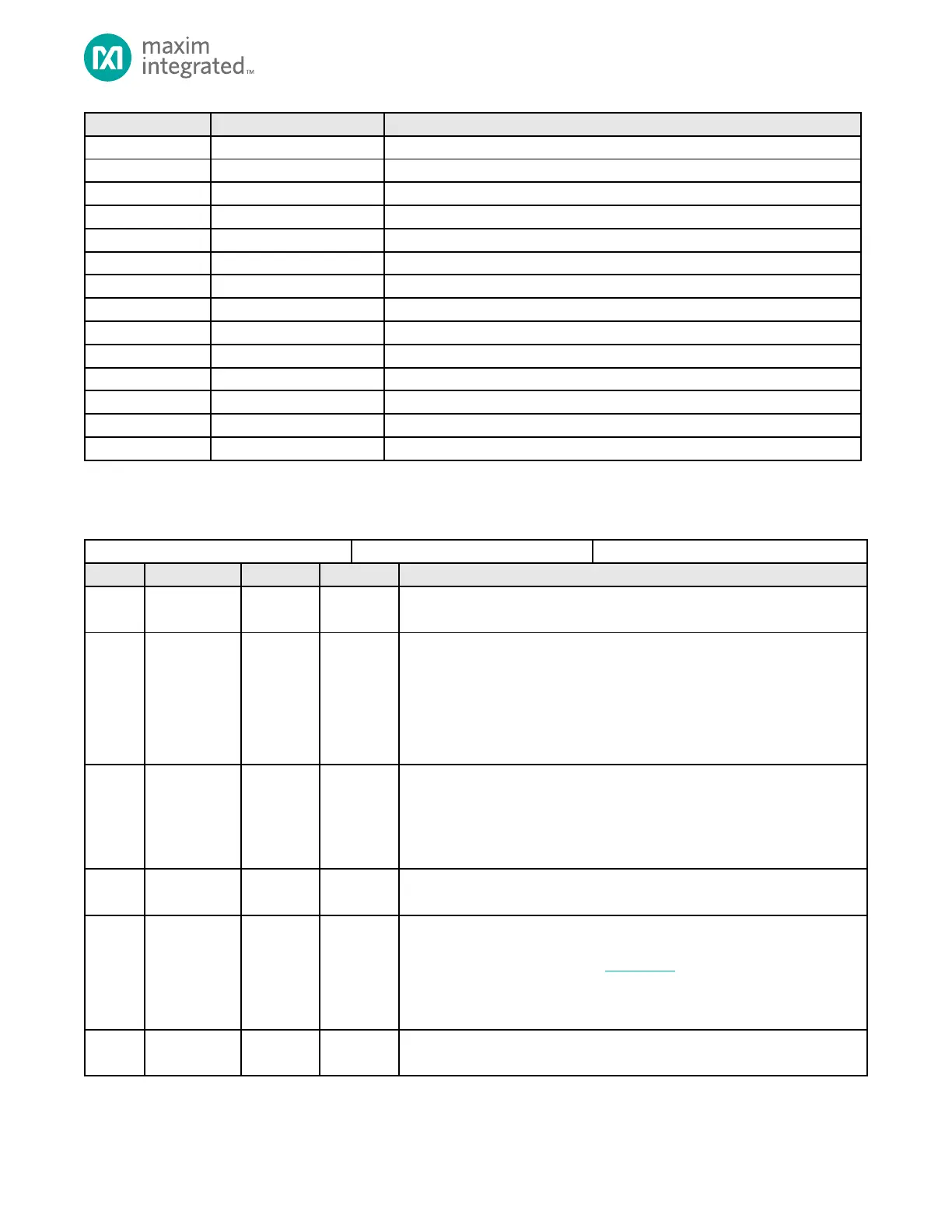

Peripheral Clocks Disable 1

System Status Interrupt Enable

Error Correction Coding Error Register

Error Correction Coding Not Double Error Detected

Error Correction Coding Interrupt Enable Register

Error Correction Coding Error Address Register

Bluetooth LDO Control Register

Bluetooth LDO Delay Count Register

Arm Peripheral Bus Asynchronous Bridge Select Register

4.17 Global Control Register Details (GCR)

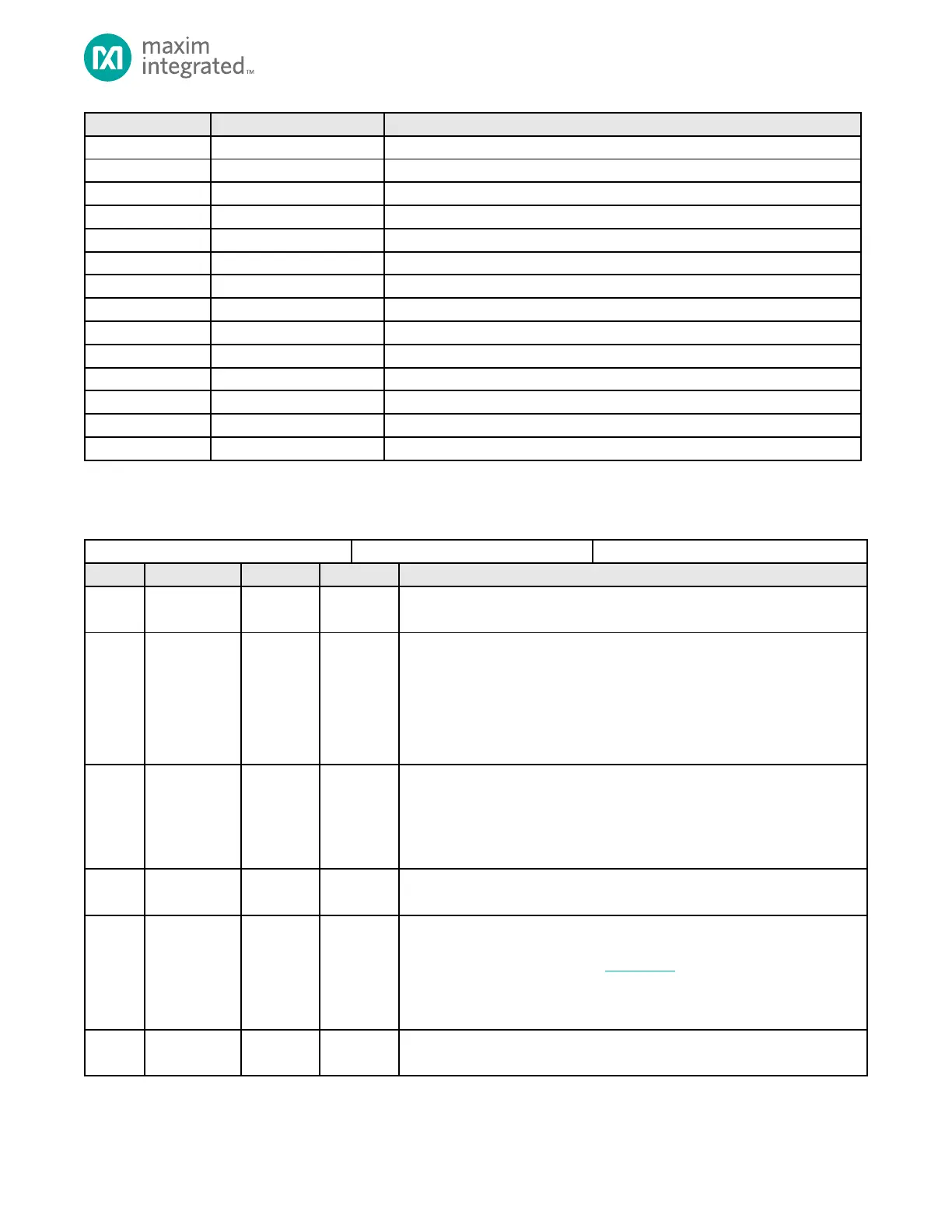

Table 4-54: System Control Register

Reserved

Do not modify this field.

Operating Voltage Range

To allow on-chip volatile memory to operate at the optimal timing range, set

this to be the same as V

COREB

.

0b00: 0.9V ±10%

0b01: 1.0V ±10%

0b10: 1.1V ±10%

0b11: Reserved.

ROM Checksum Calculation Pass/Fail

This is the result after setting bit GCR_SCON.cchk.

This bit is only valid after the ROM checksum is complete and cchk is cleared.

0: Pass

1: Fail

Reserved

Do not modify this field.

Calculate ROM Checksum

This bit is self-clearing when the ROM checksum calculation is complete,

and the result is available at bit GCR_SCON.chkres. Writing a 0 has no

effect.

0: No operation

1: Start ROM checksum calculation.

Reserved

Do not modify this field.

Loading...

Loading...