MAX32665-MAX32668 User Guide

Maxim Integrated Page 87 of 457

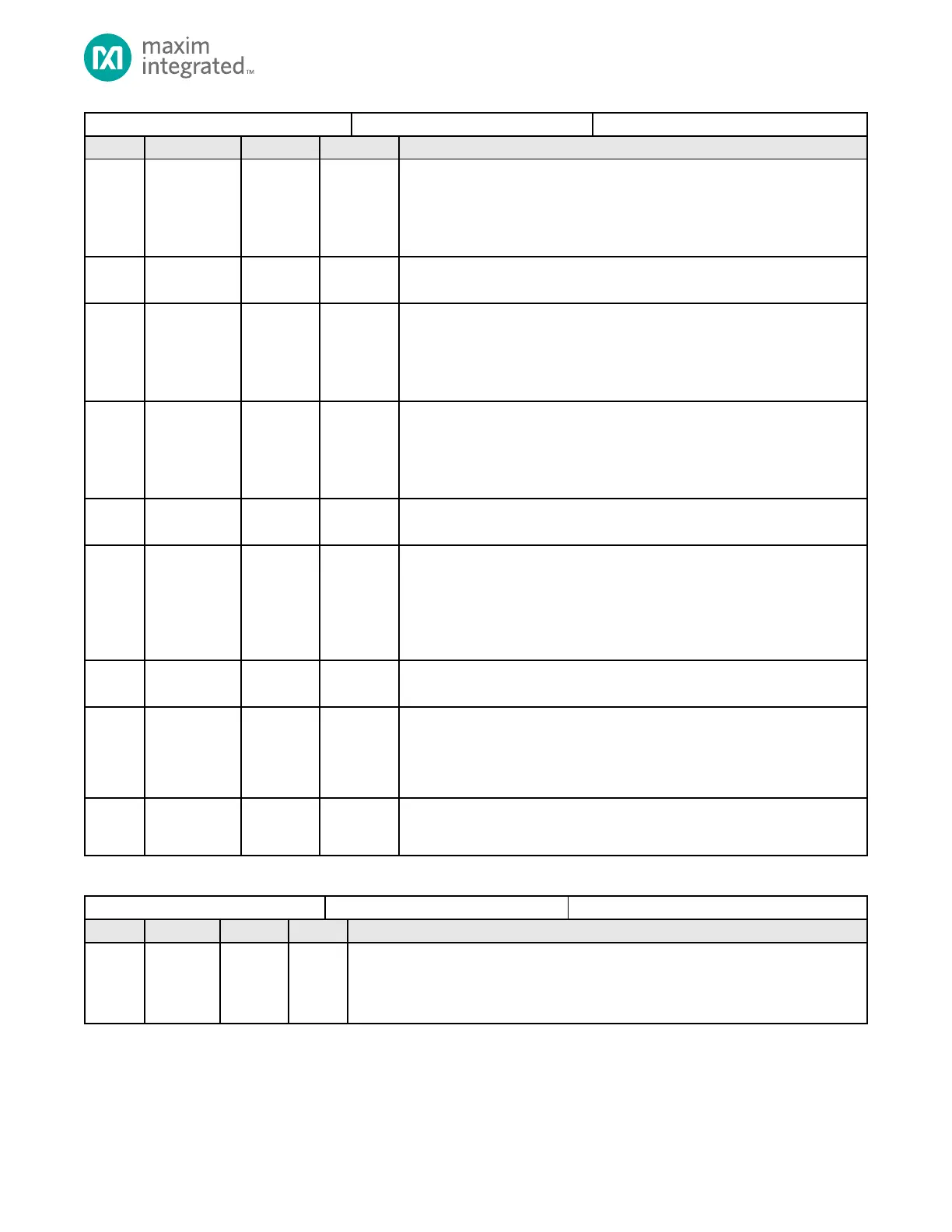

SPIXR Cache Controller (SRCC) Disable

This disables the SRCC used for SPIXR code and data cache. Setting this field

disables the cache and bypasses the cache line buffer.

0: Cache enabled

1: Cache disabled and line buffer bypassed

Reserved

Do not modify this field.

SPIXR Cache (SRCC) Flush

Write 1 to flush the SPIXR 16KB cache. This bit is automatically cleared to 0

when the flush is complete. Writing 0 has no effect.

0: Memory flush not in progress.

1: Memory flush in progress.

ICC0/ICC1/SFCC Code Cache Flush

Write 1 to flush all three caches. This bit is automatically cleared to 0 when the

flush is complete. Writing 0 has no effect.

0: Memory flush not in progress.

1: Memory flush in progress.

Reserved

Do not modify this field.

Flash Page Flip Flag

Flips the bottom and top halves of Flash memory. This bit is controlled by

hardware. Firmware should not change the state of this bit during normal

operation. Any change to this bit also flushes both code and data caches.

0: Physical layout matches logical layout

1: Top and Bottom halves flipped

Reserved

Do not modify this field.

System Bus Arbitration Scheme

00: Fixed Burst

01: Round-Robin

10: Reserved

11: Reserved

Boundary Scan Tap Enable

Reserved

Do not modify this field.

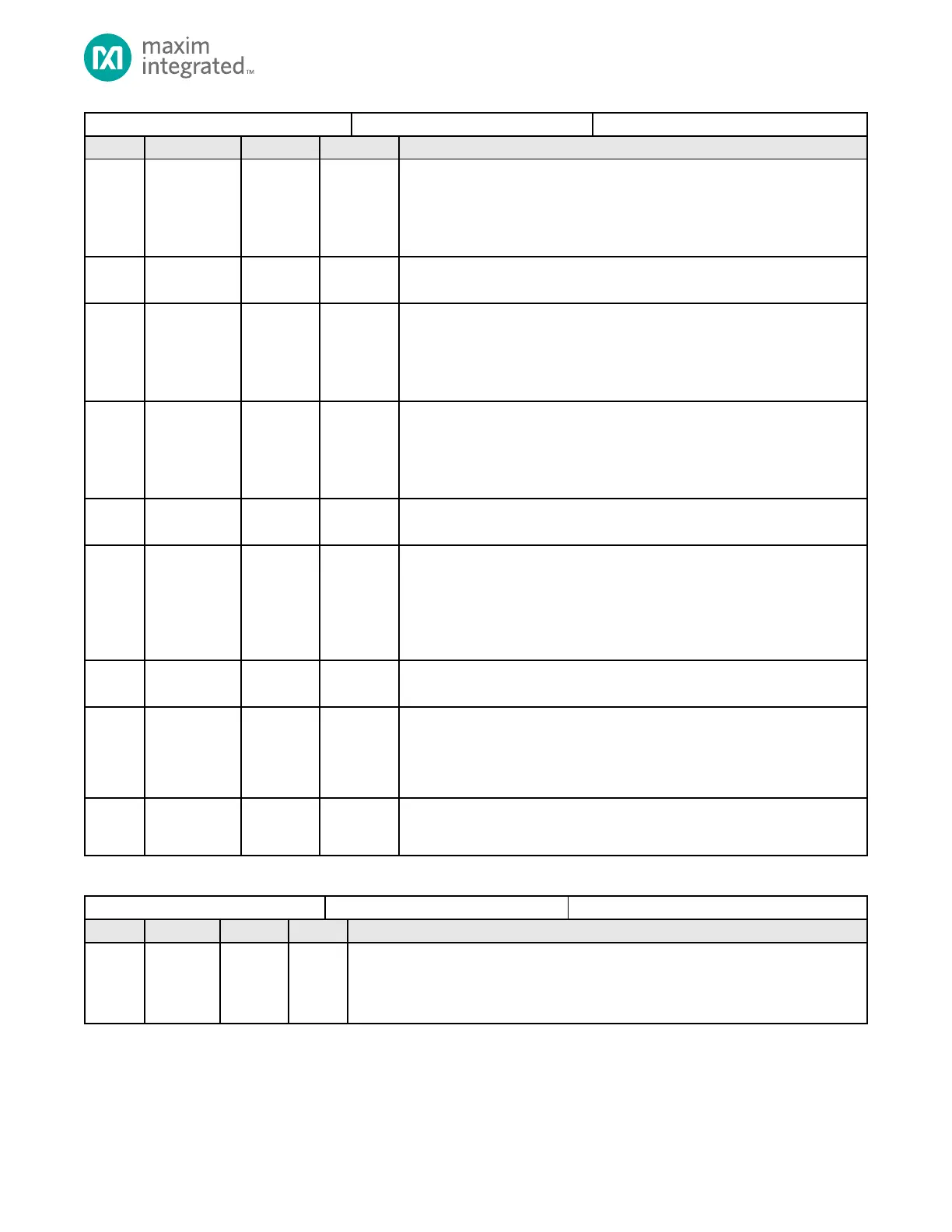

Table 4-55: Reset Register 0

System Reset

Write 1 to reset.

0: Not in reset

1: Reset in progress.

Loading...

Loading...