MAX32665-MAX32668 User Guide

Maxim Integrated Page 177 of 457

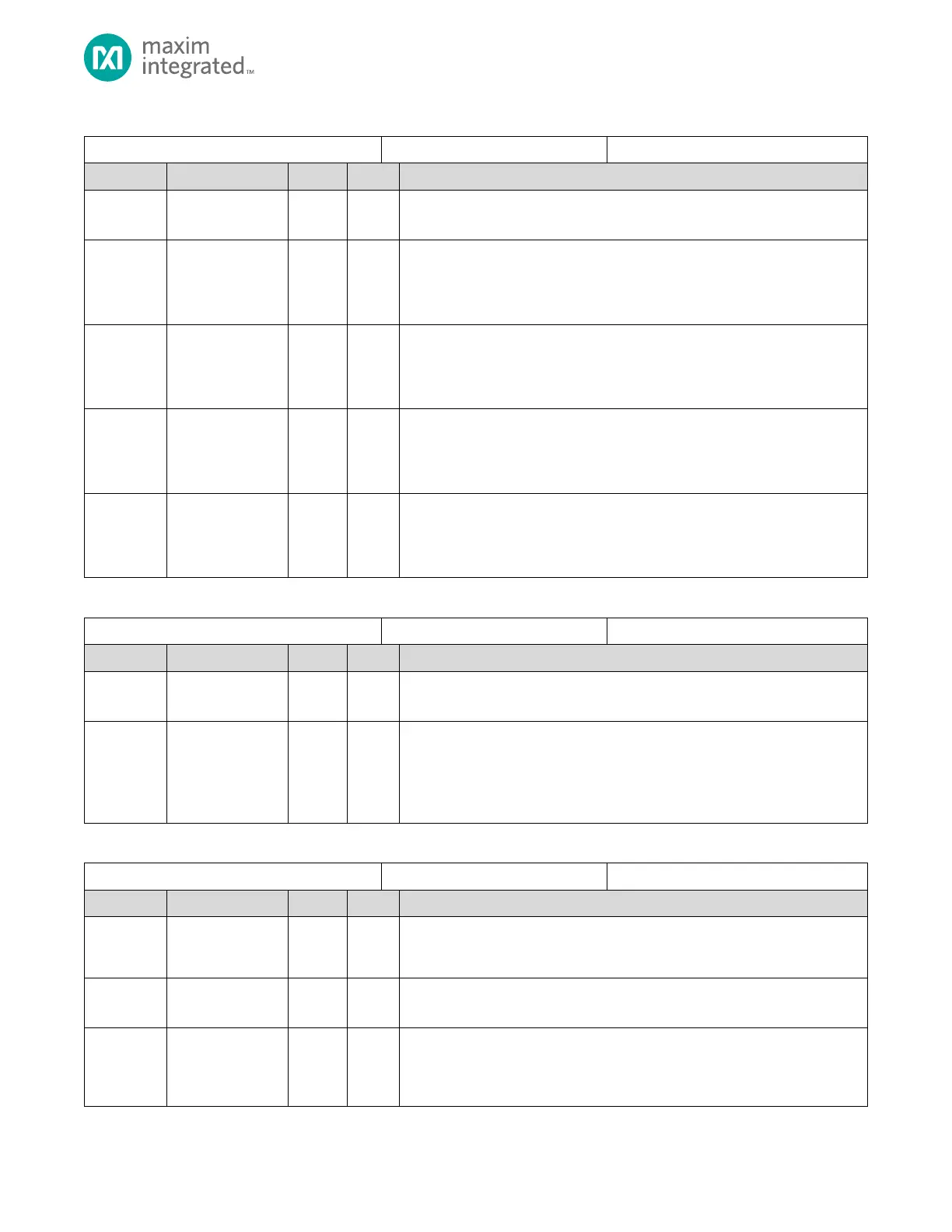

Table 8-35. SPIXR Wakeup Enable Register

SPIXR Wakeup Enable Register

Reserved for Future Use

Do not modify this field.

Wake on RX FIFO Full Enable

Set to 1 to wake up the device when this RX FIFO is full.

0: Wakeup Disabled for this condition.

1: Wakeup Enabled for this condition.

Wake on RX FIFO Threshold Level Crossed Enable

Set to 1 to wake up the device when this RX FIFO is full.

0: Wakeup Disabled for this condition.

1: Wakeup Enabled for this condition.

Wake on TX FIFO Empty Enable

Set to 1 to wake up the device when this RX FIFO is full.

0: Wakeup Disabled for this condition.

1: Wakeup Enabled for this condition.

Wake on TX FIFO Threshold Level Crossed Enable

Set to 1 to wake up the device when this RX FIFO is full.

0: Wakeup Disabled for this condition.

1: Wakeup Enabled for this condition.

Table 8-36. SPIXR Active Status Register

SPIXR Active Status Register

Reserved for Future Use

Do not modify this field.

SPI Active Status

This field returns the status of the SPIXR communications. Hardware sets and

clears this field automatically when SPI communications are active or complete.

0: SPI is not active. Cleared when the last character is sent.

1: SPI is active. Set when transmit starts.

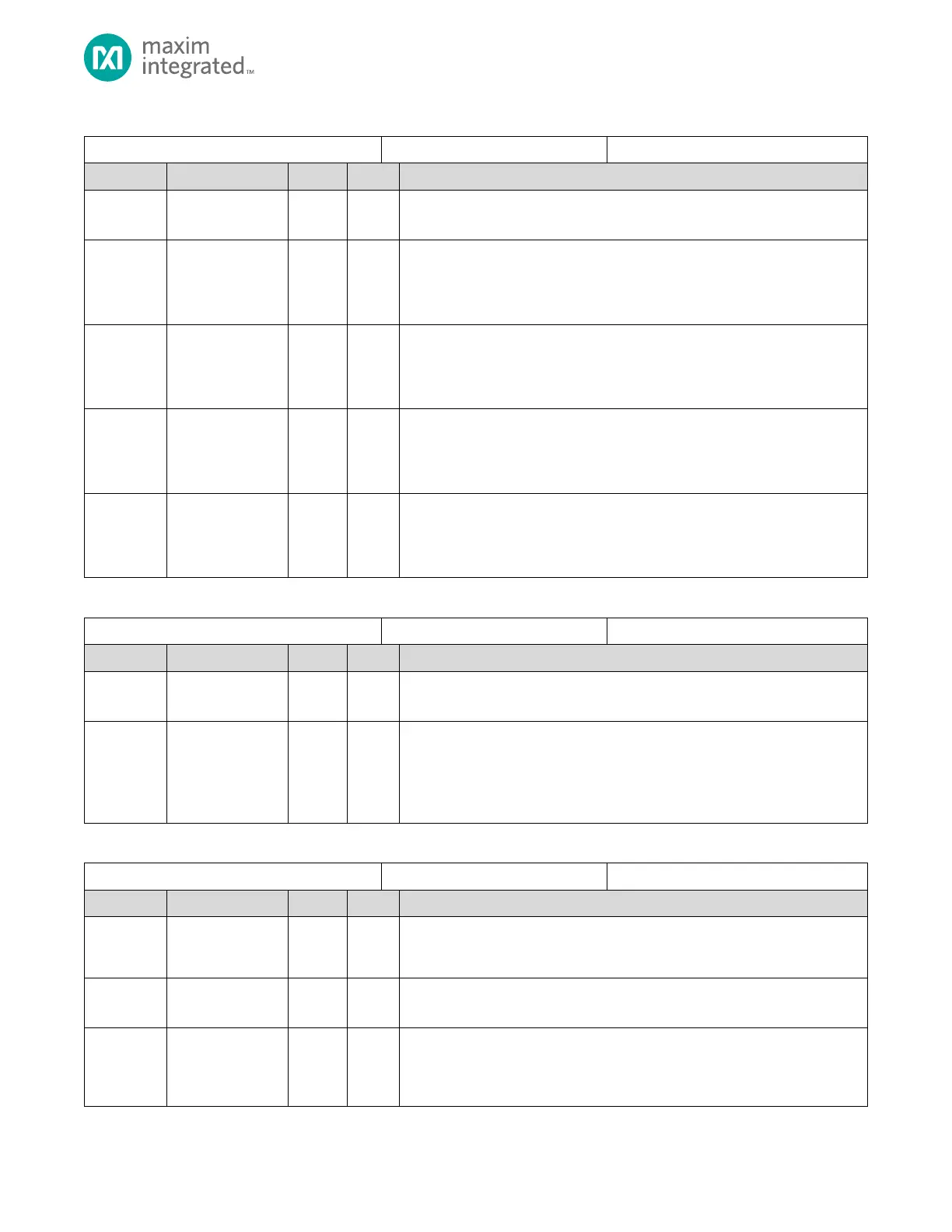

Table 8-37. SPIXR External Memory Control Register

SPIXR External Memory Control Register

Enable External Memory

0: XMEM disabled

1: XMEM enabled

Reserved for Future Use

Do not modify this field.

Number of dummy characters between address phase and read data from the

external memory.

0: no delay between address and read data

1:255 delay number of characters

Loading...

Loading...