MAX32665-MAX32668 User Guide

Maxim Integrated Page 258 of 457

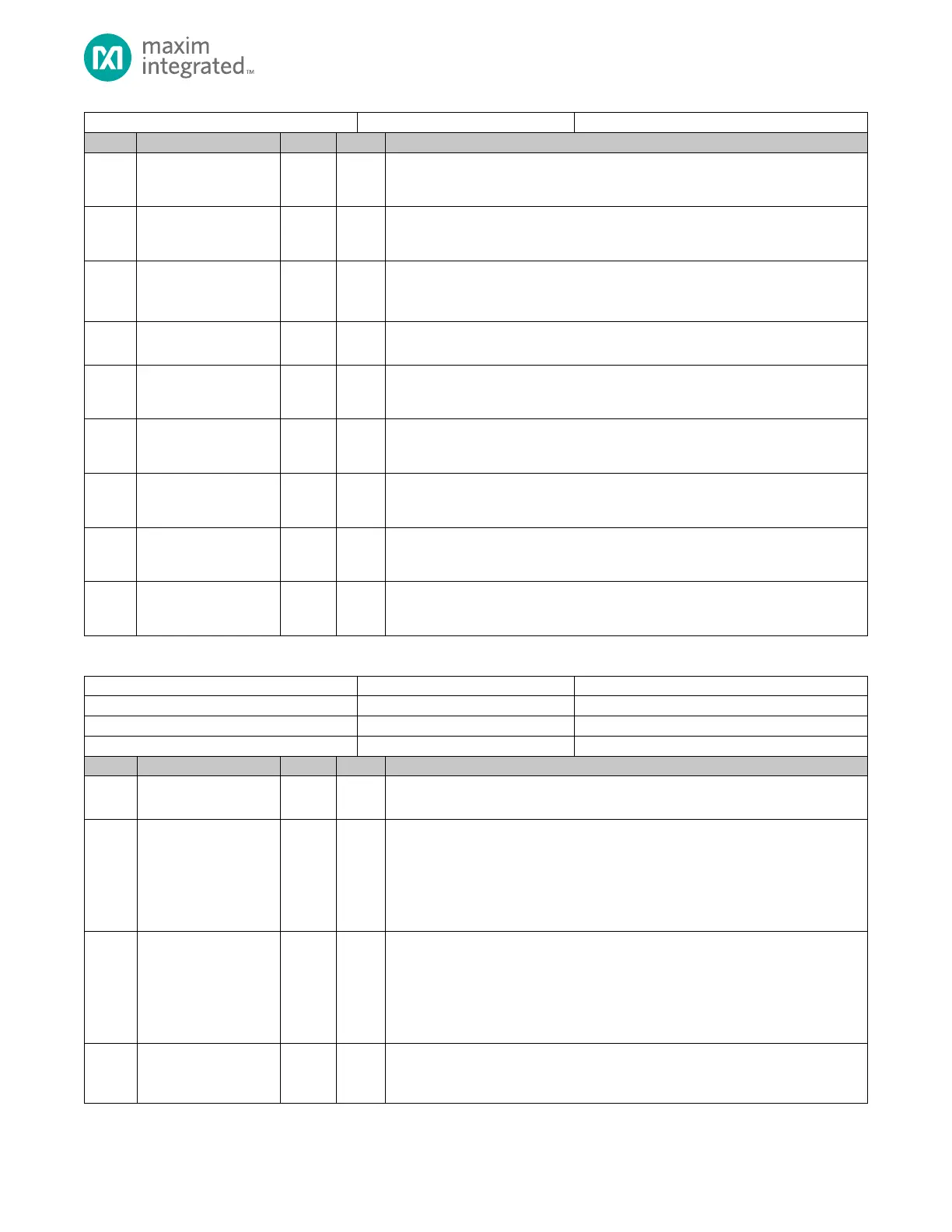

ADC High Limit Interrupt Flag

1: The last conversion resulted in a high-limit condition for one of the limit

registers.

ADC Reference Ready Interrupt Flag

0: Not Ready

1: Ready.

ADC Conversion Complete Interrupt Flag

Set by the ADC hardware when an ADC conversion is complete.

1: ADC conversion complete

Reserved for Future Use

Do not modify this field.

ADC Overflow Interrupt Enable

0: Disabled.

1: Enables interrupt assertion when hardware sets ADC_INTR.overflow_if.

ADC Low Limit Interrupt Enable

0: Disabled.

1: Enables interrupt assertion when hardware sets the ADC_INTR.lo_limit_if.

ADC High Limit Interrupt Enable

0: Disabled.

1: Enables interrupt assertion when hardware sets ADC_INTR.lo_limit_if.

ADC Reference Ready Interrupt Enable

0: Disabled.

1: Enables interrupt assertion when hardware sets ADC_INTR.ref_ready_if.

ADC Conversion Complete

0: Disabled.

1: Enables interrupt assertion when hardware sets ADC_INTR.done_if.

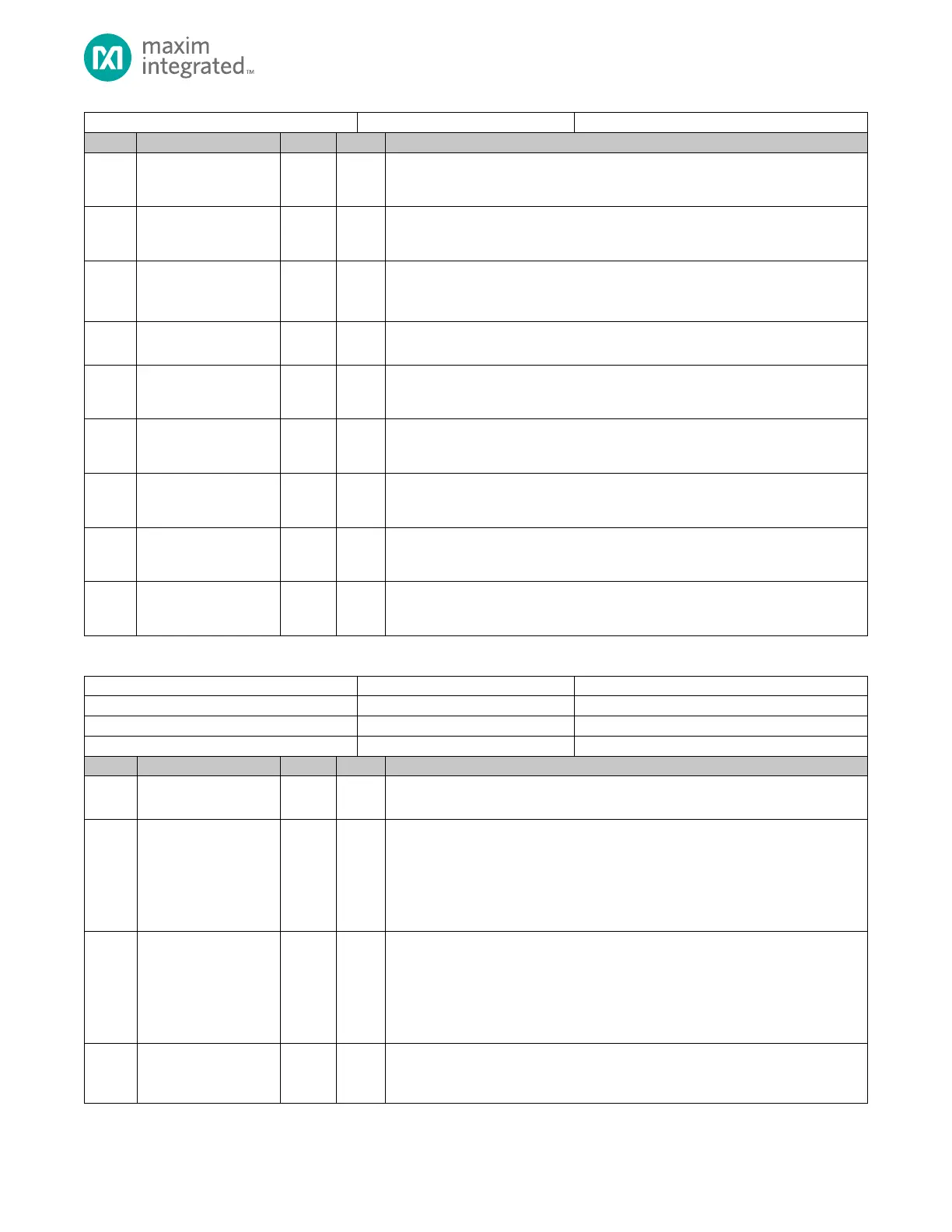

Table 11-10: ADC Limit 0 to 3 Registers

Reserved for Future Use

Do not modify this field.

High Limit Monitoring Enable

If set, then an ADC conversion that results in a value greater than the ch_high_limit

field generates an ADC interrupt if the ADC high-limit interrupt is enabled.

(ADC_INTR.hi_limit_ie = 1).

1: The high-limit comparison for the ch_sel channel is active.

0: The high-limit comparison is not enabled.

Low Limit Monitoring Enable

If set, then an ADC conversion that results in a value less than the ch_high_limit

field generates an ADC interrupt if the ADC low-limit interrupt is enabled

(ADC_INTR.lo_limit_ie = 1).

1: The low-limit comparison for the ch_sel channel is active.

0: The low-limit comparison is not enabled.

ADC Channel for Limit Monitoring

Sets the ADC input channel for high- and low-limit thresholds. See ADC_CTRL

for valid values for this field.

Loading...

Loading...