MAX32665-MAX32668 User Guide

Maxim Integrated Page 205 of 457

Table 8-74: Transfer Complete and Data Timeout Error Priority and Status

Transfer Complete

SDHC_INT_STAT.trans_comp

Data Timeout Error

SDHC_ER_INT_STAT.data_to

Interrupted by another event

Timeout occurred during transfer

Command execution complete

Table 8-75: Command Complete and Command Timeout Error Priority and Status

Transfer Complete

SDHC_INT_STAT.cmd_comp

Data Time Error

SDHC_ER_INT_STAT.cmd_to

Interrupted by another event.

Response not received within 64 SD Clock cycles.

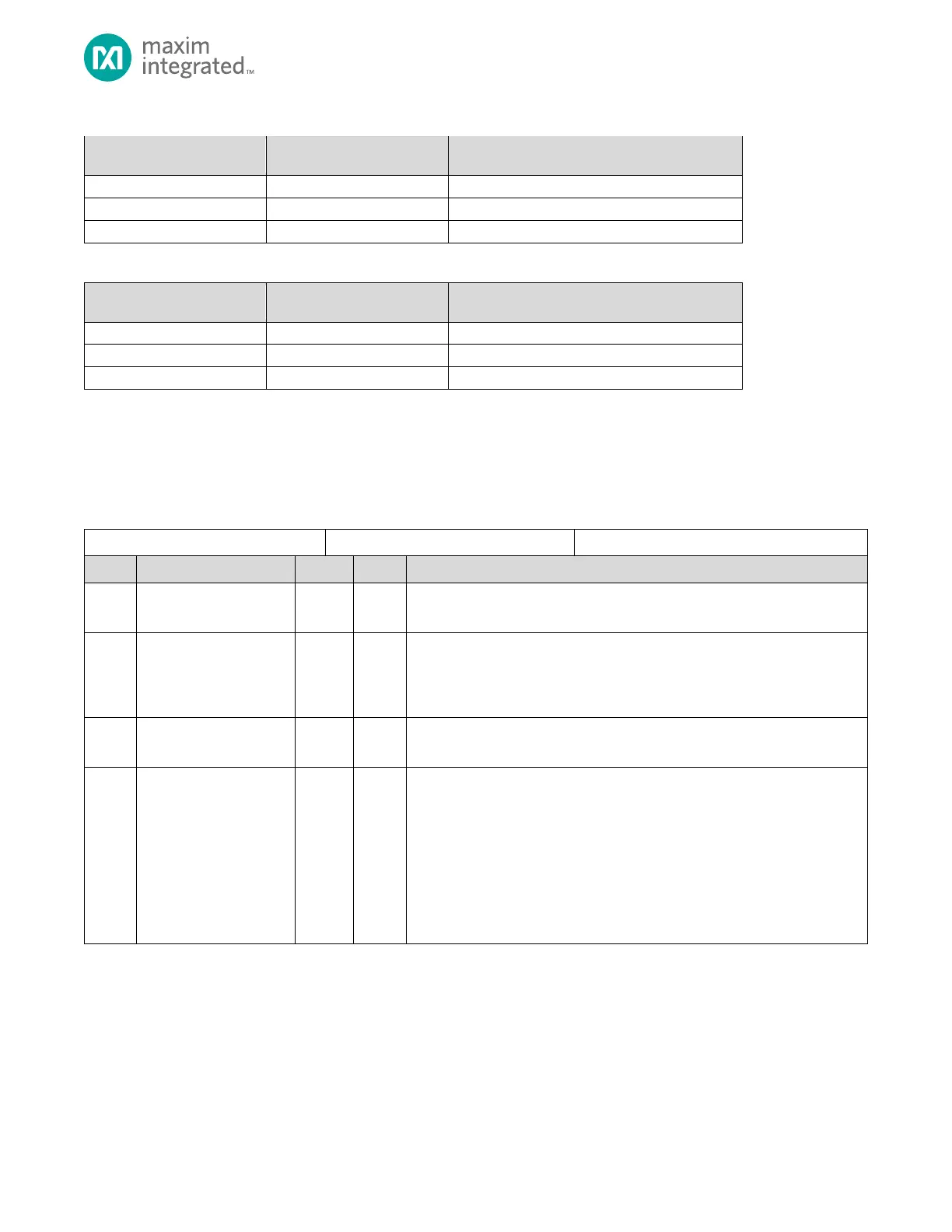

8.5.6.2 Error Interrupt Status Register

The interrupts defined in this register are enabled by the corresponding fields in the Error Interrupt Status Enable

(SDHC_ER_INT_EN) register. Setting any field in the SDHC_ER_INT_SIGNAL register enables SDHC error interrupt generation

using the SDHC_IRQ. The interrupt occurs when any field in the SDHC_ER_INT_STAT register is set to 1.

Table 8-76: SDHC Error Interrupt Status Register

Error Interrupt Status Register

Reserved for Future Use

Do not modify this field.

DMA Error

Error in SDMA transaction

1: Error

0: No error

Reserved for Future Use

Do not modify this field.

ADMA Error

Set when the SDHC detects an error during an ADMA data transfer. The state

of the ADMA when the error occurs is saved in the ADMA Error Status

(SDHC_ADMA_ER) register.

This bit is also set if the SDHC detects invalid descriptor data. If the

SDHC_ADMA_ER register indicates an ADMA Error State, then an invalid

descriptor was detected.

1: Error

0: No error

Loading...

Loading...