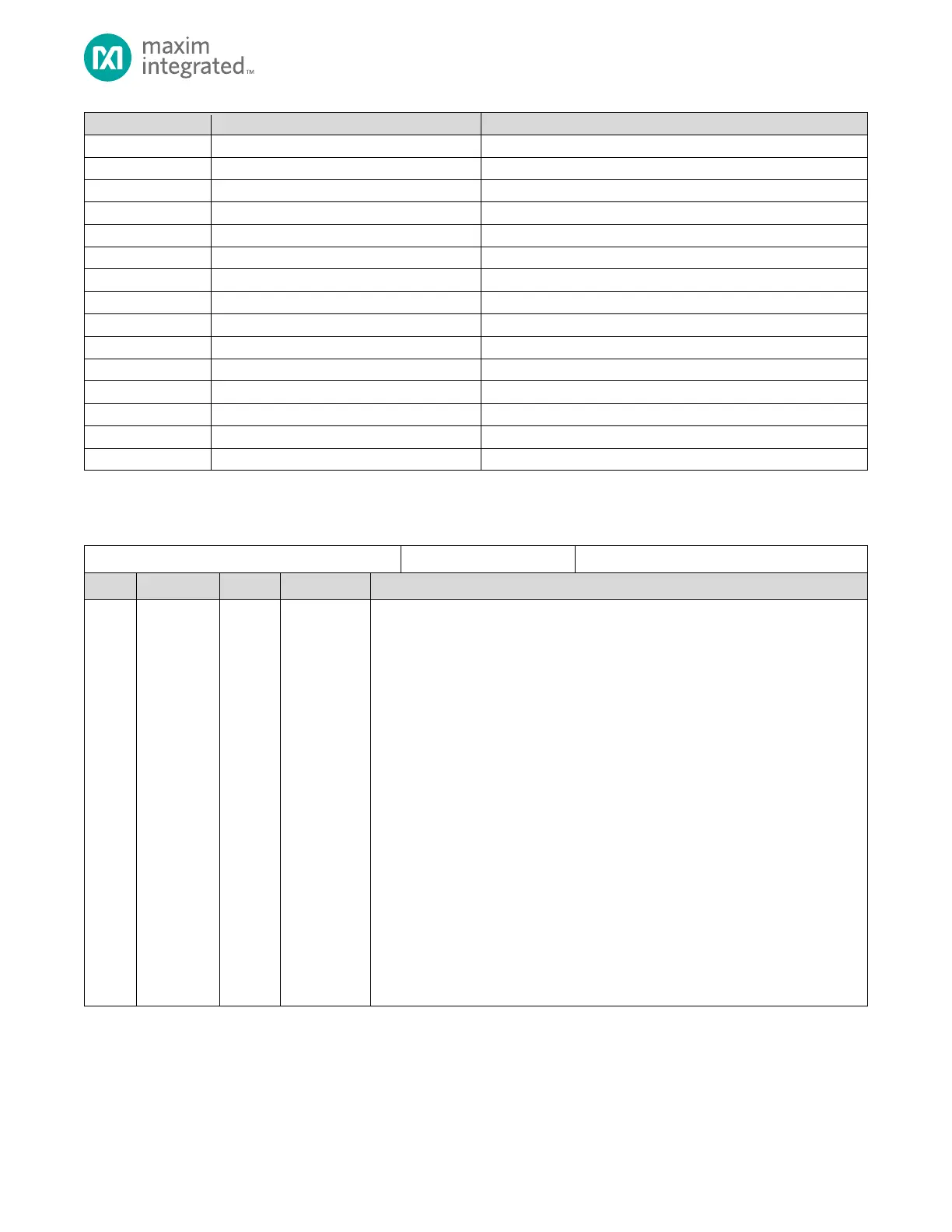

SDMA System Address

This register is the address of the buffer used for a SDMA transfer. You must set this

register to a valid data buffer address prior to starting an SDMA transfer. A SDHC DMA

interrupt (SDHC_INT_STAT.dma = 1) is generated if the total size of the SDMA transfer

exceeds the Host SDMA Buffer Size (SDHC_BLK_SIZE.host_buf). The card driver must

update the SDMA System Address (SDHC_SDMA) with the address of the next data to

transfer and clear the SDHC DMA interrupt flag prior to the transfer resuming.

When the SDMA transfer is complete, this register contains the address of the next

contiguous data address.

When resuming a SDMA transfer, using the Resume command or by setting the

SDHC_BLK_GAP.gap_cont bit to 1, the SDHC resumes using the address in this register

for the data to transfer.

Reading this register during a SDMA transfer might return an invalid value unless the

transfer is paused as the result of a SDHC DMA interrupt. This field is not used for

ADMA transfers.

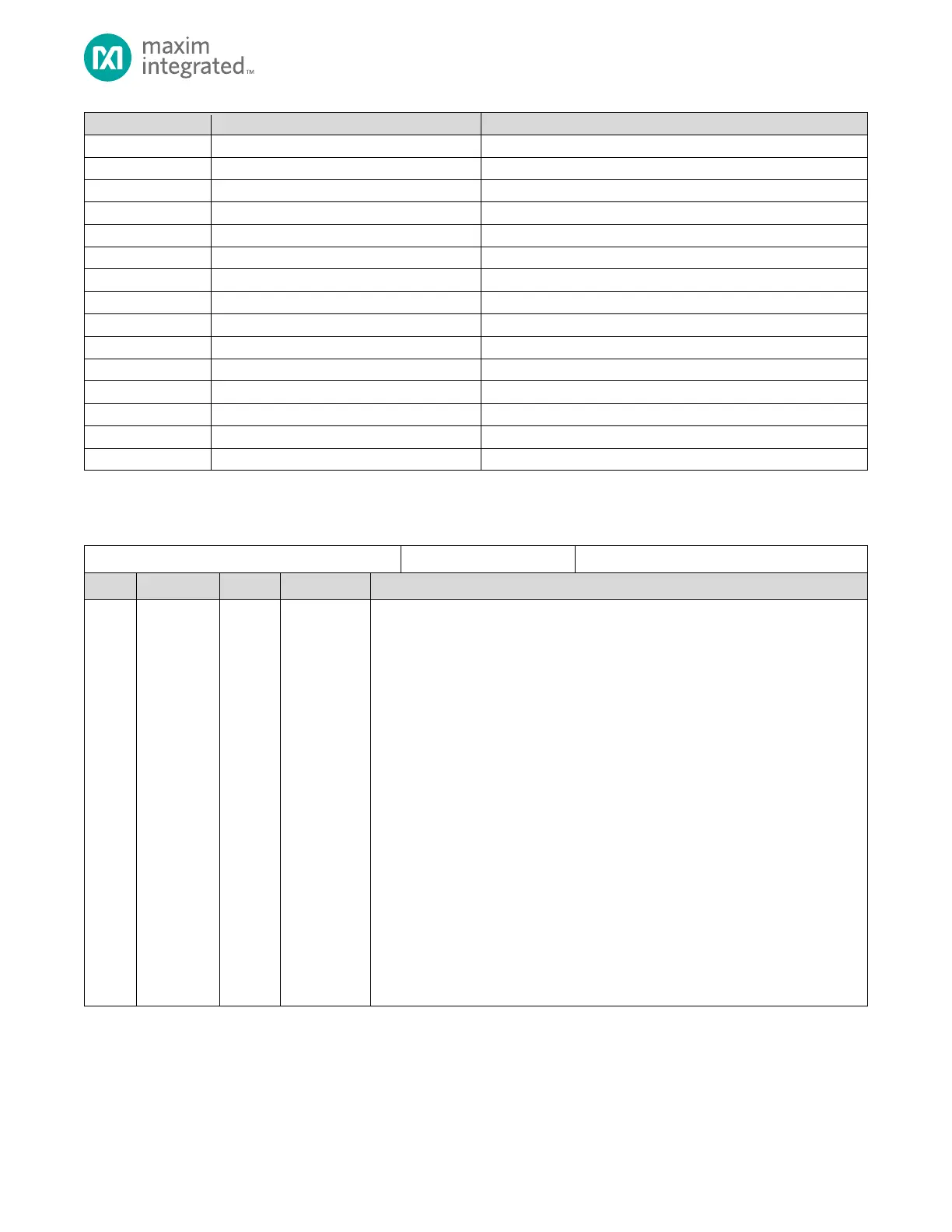

Argument 2

This register is used with Auto CMD23 to set a 32-bit block count value to the

argument of CMD23 while executing Auto CMD23.

If Auto CMD23 is used with ADMA, then the full 32-bit block count value is used. If

Auto CMD23 is used without AMDA, the available block count value is limited by the

SDHC_BLK_GAP register to 65,535 blocks.

Loading...

Loading...