MAX32665-MAX32668 User Guide

Maxim Integrated Page 144 of 457

data in the Transmit FIFO. At the end of every SPI transfer, data is moved from the shift register into the Receive FIFO.

Status flags and interrupts are available to monitor the data levels in these FIFOs.

When a SPI transfer occurs, a multi-byte (selectable from 1 to 1024bytes) packet is shifted out if the Transmit FIFO has

configured the device to transmit using the Transmit FIFO header entry. The most significant bit is sent first. If the Transmit

FIFO configures the device to receive, the device receives data most significant bit first, and places each byte received into

the Receive FIFO.

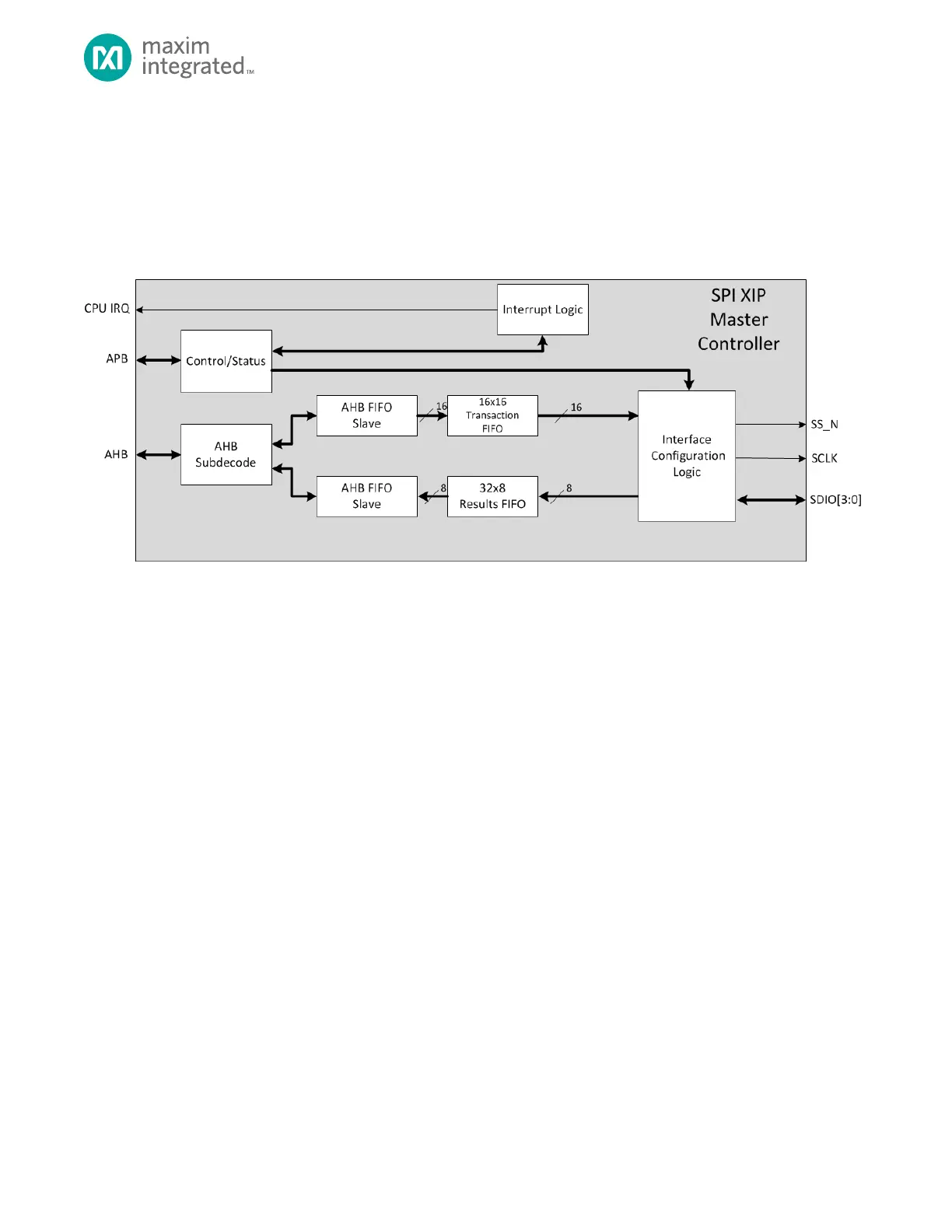

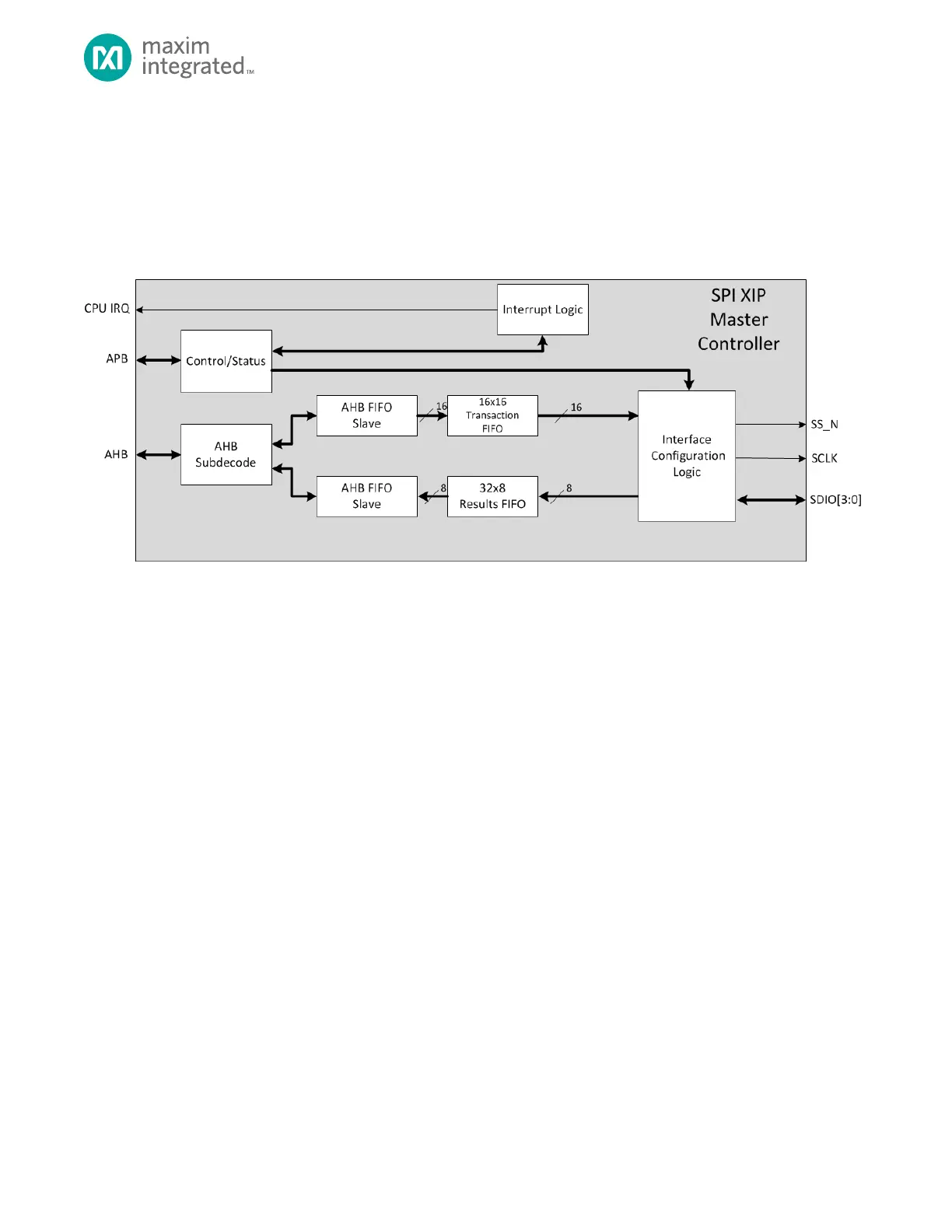

Figure 8-2. Simplified Block Diagram

8.2.1.1 SPIXFC Configuration

The SPIXF Master Controller shares pins with the SPIXF Master so that the SPI flash is configured for code execution or data

transfer. See the SPI Pins Configuration section of the SPIXF Master for more information.

8.2.1.1.1 Configuration Modes Overview

Once the main SPIXF Master Controller clock is set up, the remainder of the configuration and operation for this block is

mapped into three categories:

1. Static configuration: Performed during SPI initial setup, when the communicate port is disabled, or both.

a. SPIXFC_GEN_CTRL register: SCK Feedback mode, enable Transmit and Receive FIFOs

b. SPIXFC_SS_POL register: Slave Select signal polarity

c. SPIXFC_CFG register: Active slave, SPI clock polarity and phase that is, mode), clock and slave select timing.

2. Dynamic configuration: Configuration required to communicate with a specific slave device, which may take place

while the communication port is enabled but the slave select is de-asserted.

a. SPIXFC_CFG register: SPI page transfer size if using pages. See header information in Table 8-1.

3. Interrupt servicing: Status and control used by an application to efficiently service the SPI data transfer.

a. SPIXFC_FIFO_CTRL register: Transmit and Receive FIFO monitoring levels

b. SPIXFC_INT_FL register: Interrupt flag bits

c. SPIXFC_INT_EN register: Interrupt enable bits

8.2.1.1.2 SPI Master Controller Transaction

Once the SPIXFC is configured to communicate to a specific slave, SPI transactions are initiated by writing to the SPI

Transmit FIFO SPIXFC_FIFO_TX. The FIFO is 16-bits wide and expects a 16-bit header followed by an optional payload

padded out to a word boundary

Loading...

Loading...