MAX32665-MAX32668 User Guide

Maxim Integrated Page 132 of 457

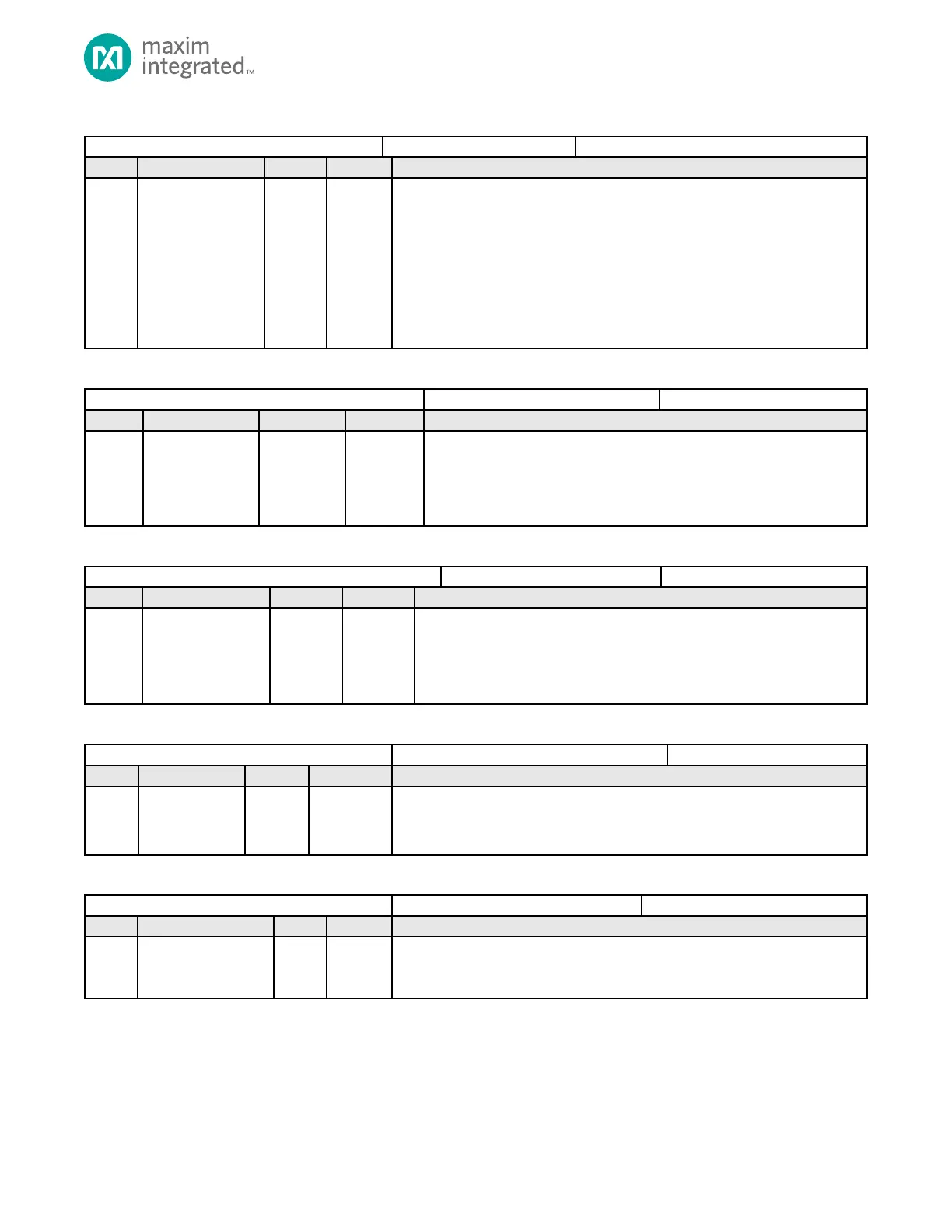

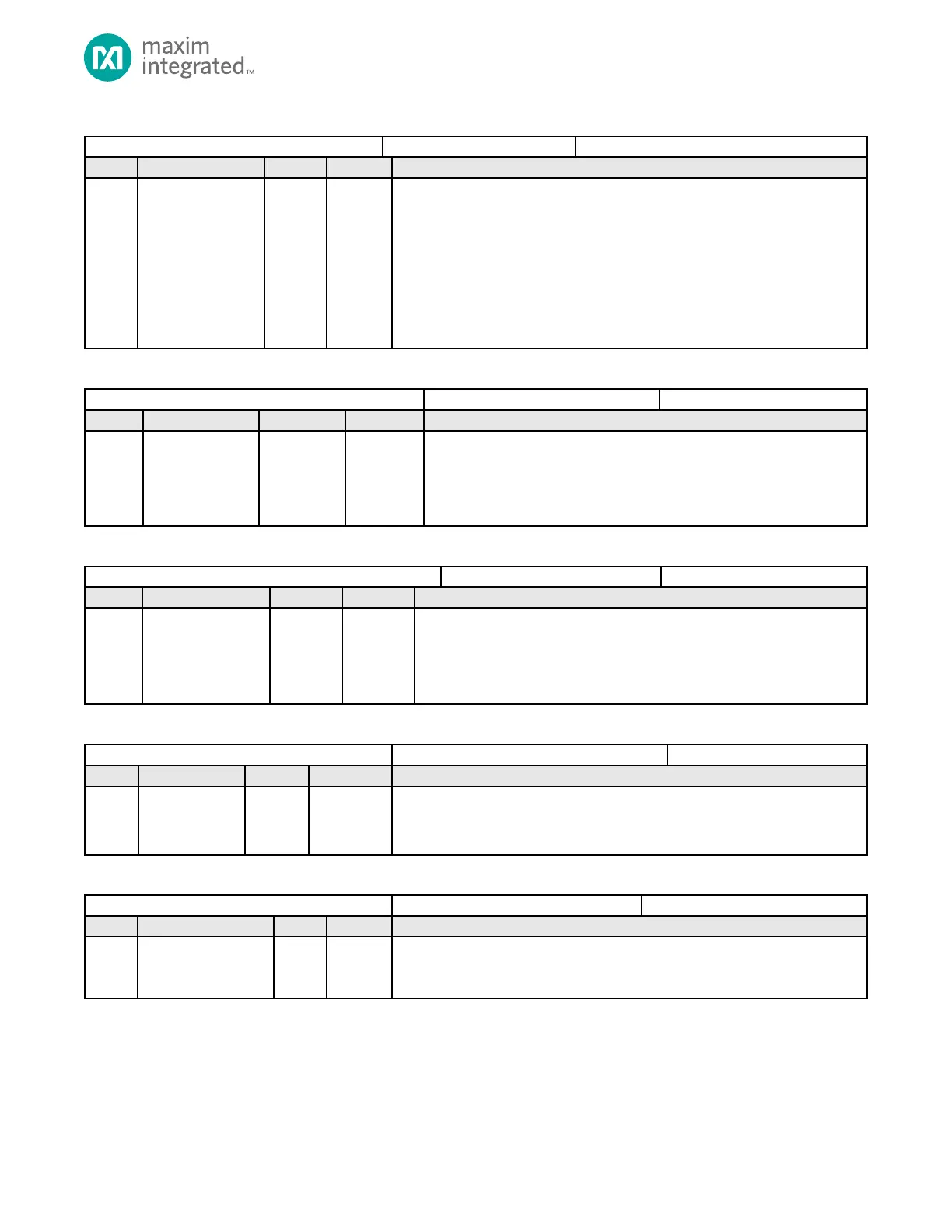

Table 6-36: GPIO Port n Configuration Enable Bit 2 Register

GPIO Port n Configuration Enable Bit 2

GPIO Configuration Enable, Bit 2

This bit, in conjunction with bits in Table 6-3: MAX32665—MAX32668 GPIO Pin

Configuration, configures the corresponding device pin as a GPIO or an alternate

function mode.

Some GPIO are not implemented all devices. The bits associated with

unimplemented GPIO should not be changed from their default value. See Table

6-1: MAX32665—MAX32668 GPIO Pin Count concerning which pins are available.

This bit’s setting does not affect input and interrupt functionality of the

associated pin.

Table 6-37: GPIO Port n Configuration Enable Atomic Set Bit 2 Register

GPIO Port n Configuration Enable Atomic Set Bit 2

GPIO Alternate Function Select Atomic Set, Bit 2

Writing 1 to one or more bits sets the corresponding bits in the GPIOn_EN2

register.

0: No effect.

1: Corresponding bits in GPIOn_EN2 register set to 1.

Table 6-38: GPIO Port n Configuration Enable Atomic Clear Bit 2 Register

GPIO Port n Configuration Enable Atomic Clear Bit 2

GPIO Alternate Function Select Atomic Clear, Bit 2

Writing 1 to one or more bits clears the corresponding bits in the GPIOn_EN2

register.

0: No effect.

1: Corresponding bits in GPIOn_EN2 register cleared to 0.

Table 6-39: GPIO Port n Output Drive Strength Bit 0 Register

GPIO Port n Output Drive Strength Bit 0

GPIO Output Drive Strength Selection 0

See Table 6-5: MAX32665—MAX32668 Output Mode Configuration for details on

how to set the GPIO output drive strength and other electrical characteristics.

Table 6-40: GPIO Port n Output Drive Strength Bit 0 Register

GPIO Port n Output Drive Strength Bit 1

GPIO Output Drive Strength Selection 1

See Table 6-5: MAX32665—MAX32668 Output Mode Configuration for details on

how to set the GPIO output drive strength and other electrical characteristics.

Loading...

Loading...