MAX32665-MAX32668 User Guide

Maxim Integrated Page 400 of 457

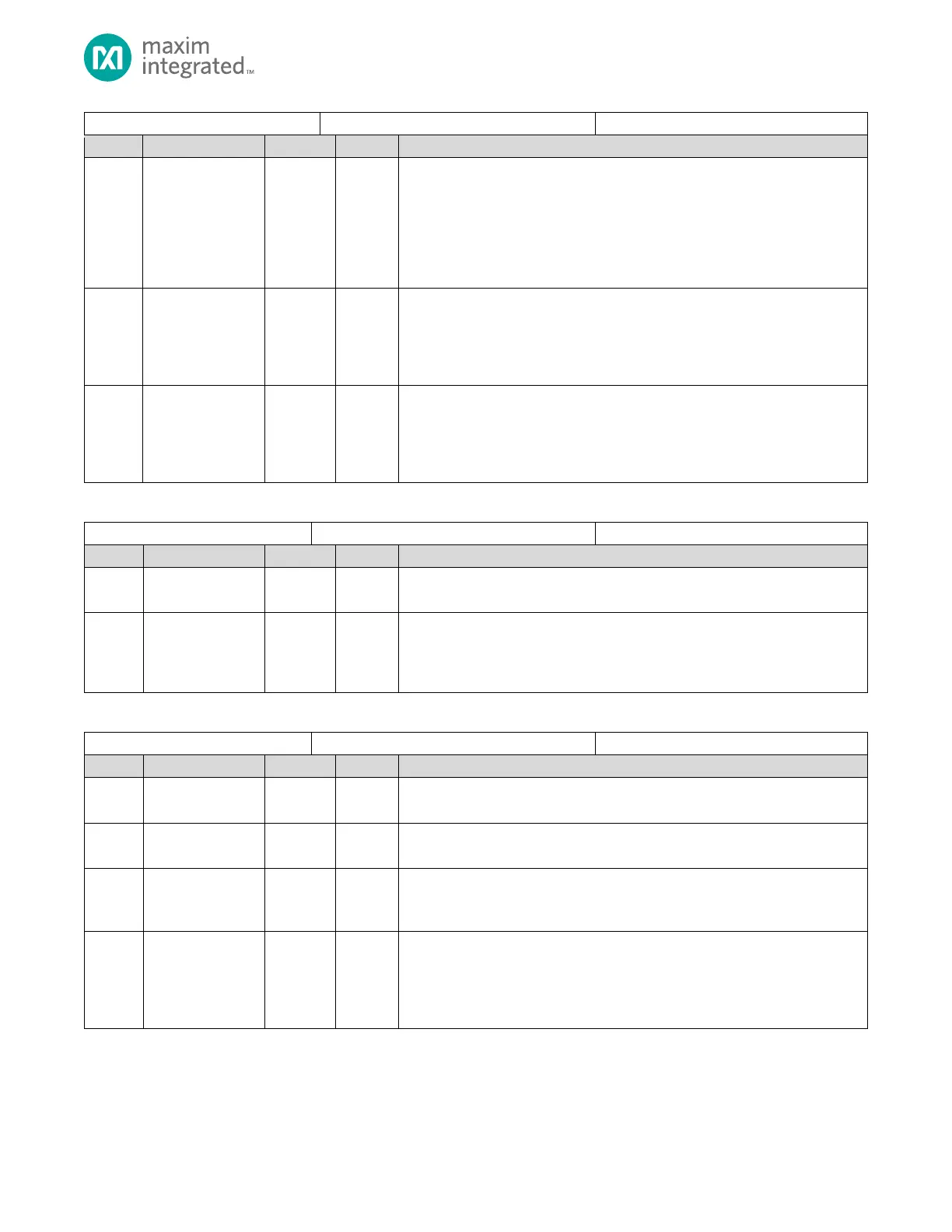

OWM Control/Status Register

OWM Bit-Bang Output

When bit-bang mode is enabled (OWM_CFG.bit_bang_en = 1), this bit sets the

state of the OWM_IO pin. Setting this bit to 1 drives the OWM_IO pin low.

Setting this bit to 0 releases the line, allowing the OWM_IO pin to be pulled high

by the pullup resistor or held low by a slave device.

0: OWM_IO pin floating.

1: Drive OWM_IO pin to low state.

Search ROM Accelerator Enable

Enable Search ROM Accelerator mode. This mode is used to identify slaves and

their addresses that are attached to the 1-Wire bus.

0: Search ROM accelerator mode disabled.

1: Search ROM accelerator mode enabled.

Start 1-Wire Reset Pulse

Write 1 to start a 1-Wire reset sequence. Automatically cleared by the OWM

hardware when the reset sequence is complete.

0: 1-Wire reset sequence complete or inactive.

1: Start a 1-Wire reset sequence.

Table 20-8: OWM Data Register

Reserved for Future Use

Do not modify this field.

OWM Data Field

Writing to this field sets the transmit data and initiates a 1-Wire data transmit

cycle. Reading from this field returns the data received by the master during the

last 1-Wire data transmit cycle.

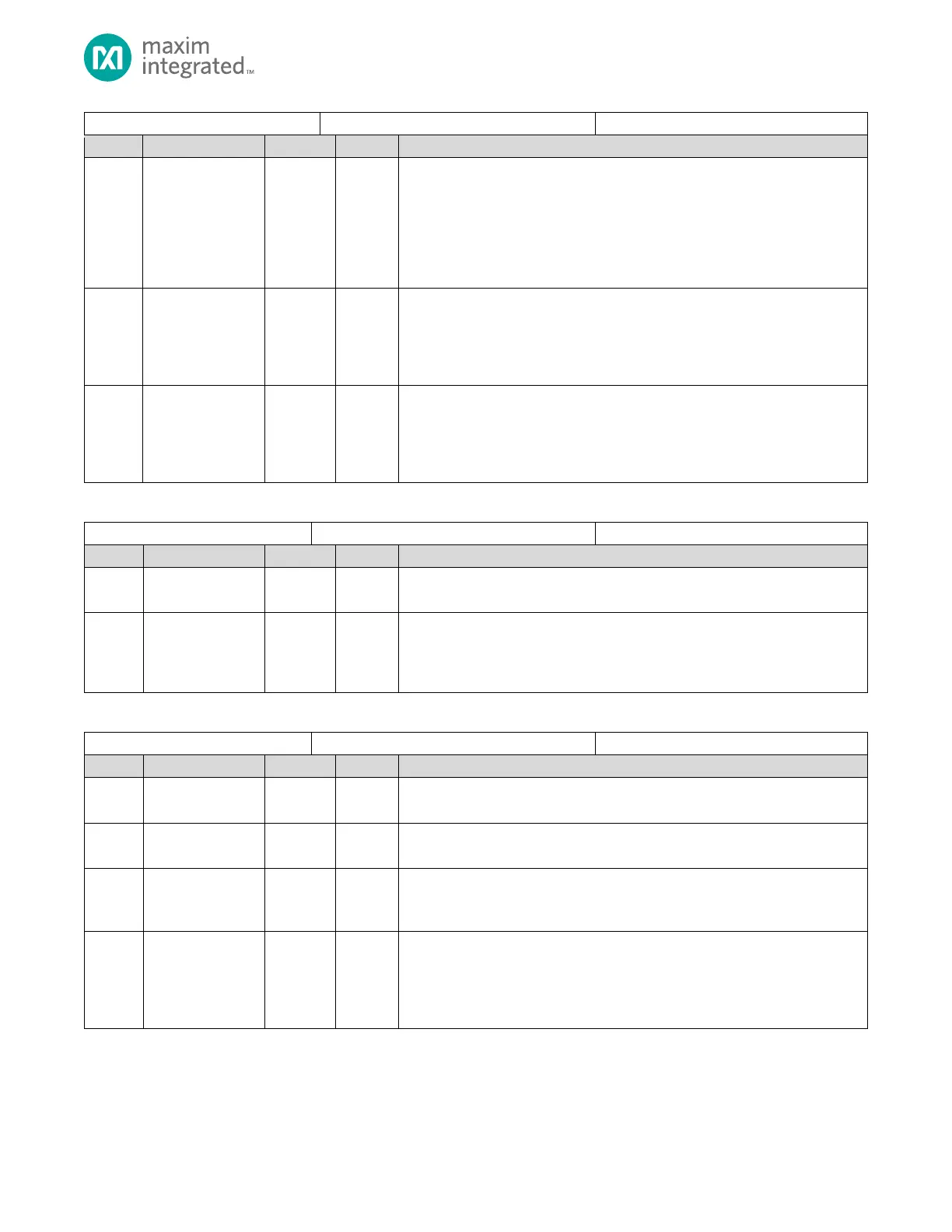

Table 20-9: OWM Interrupt Flag Register

OWM Interrupt Flag Register

Reserved for Future Use

Do not modify this field.

Line Low Flag

If this flag is set, the OWM_IO pin was in a low state. Write 1 to clear this flag.

Line Short Flag

The OWM hardware detected a short on the OWM_IO pin. Write 1 to clear this

flag.

RX Data Ready

Data received from the 1-Wire bus and is available in the OWM_DATA.tx_rx

field. Write 1 to clear this flag.

0: RX data not available.

1: Data received and is available in the OWM_DATA.tx_rx field.

Loading...

Loading...