MAX32665-MAX32668 User Guide

Maxim Integrated Page 26 of 457

2. Resource Protection Unit (RPU)

The resource protection unit (RPU) is a dedicated module that augments the Arm Cortex-M4 core memory protection unit

(MPU). The RPU allows the system to provide resource protection for AHB bus masters accessing system memory or

AHB/APB bus slaves.

The MPU enforces privilege and access controls that restrict a CPU from accessing user-defined segments of system

memory. It does not, however, provide access controls for other AHB bus masters accessing system memory or AHB/APB

bus slaves.

The RPU is separate to and maintains software compatibility with Arm’s MPU privilege levels on the CPU side and uses the

standard AMBA bus.

The RPU features include the following:

• Software compatibility with Arm Memory Protection Unit (MPU)

• Provides access control for DMA and other AHB masters

• Access controls for each bus slave independently configurable

• Dedicated access-protection register for each bus slave

2.1 Instances

The IC has three buses:

• AHB

• APB Bus 0

• APB Bus 1

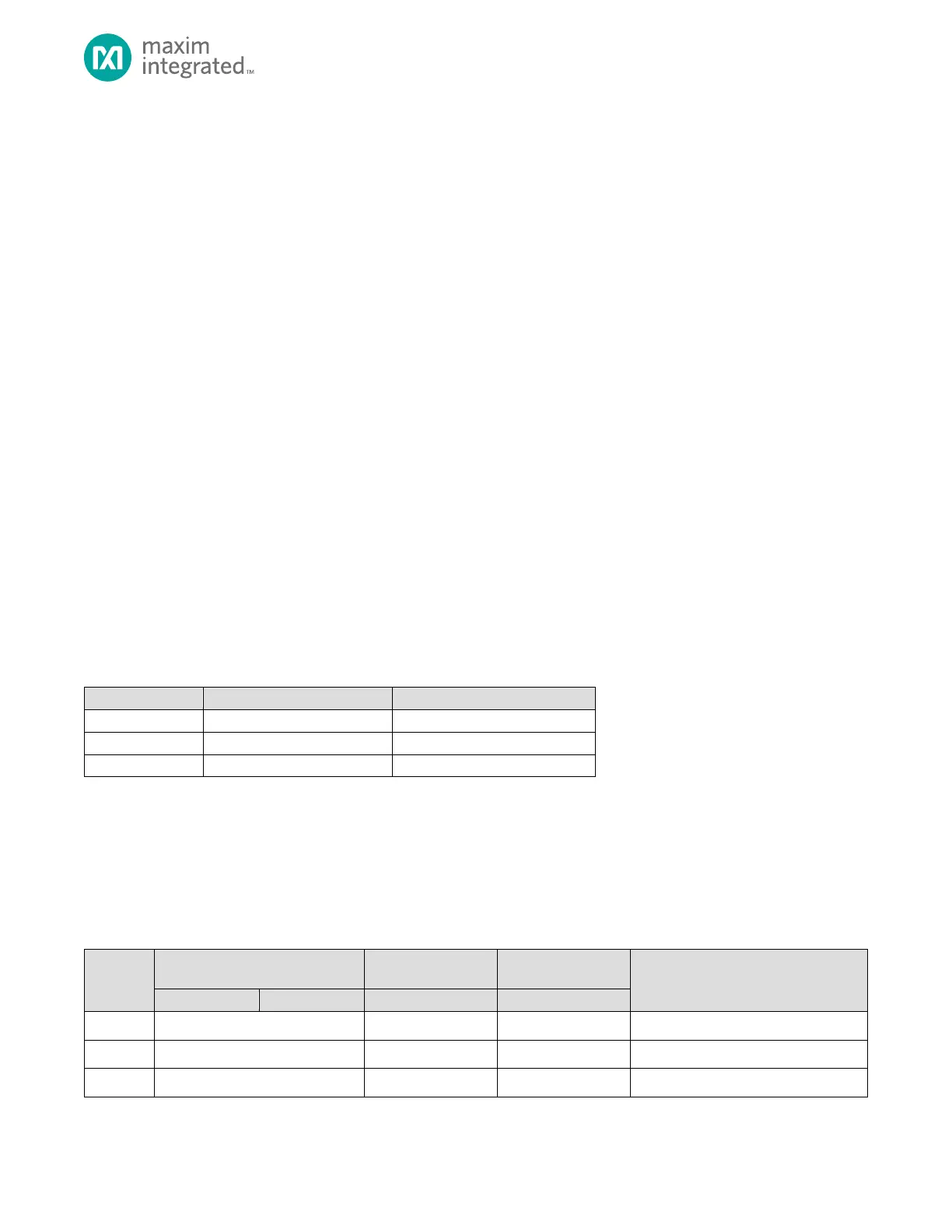

The peripherals in Table 2-1 can be mapped to either APB Bus 0 or the fixed frequency APB Bus 1. Each peripheral has a

different register set depending on the which bus the peripheral is connected to.

Table 2-1: Dual Mapped APB Peripherals

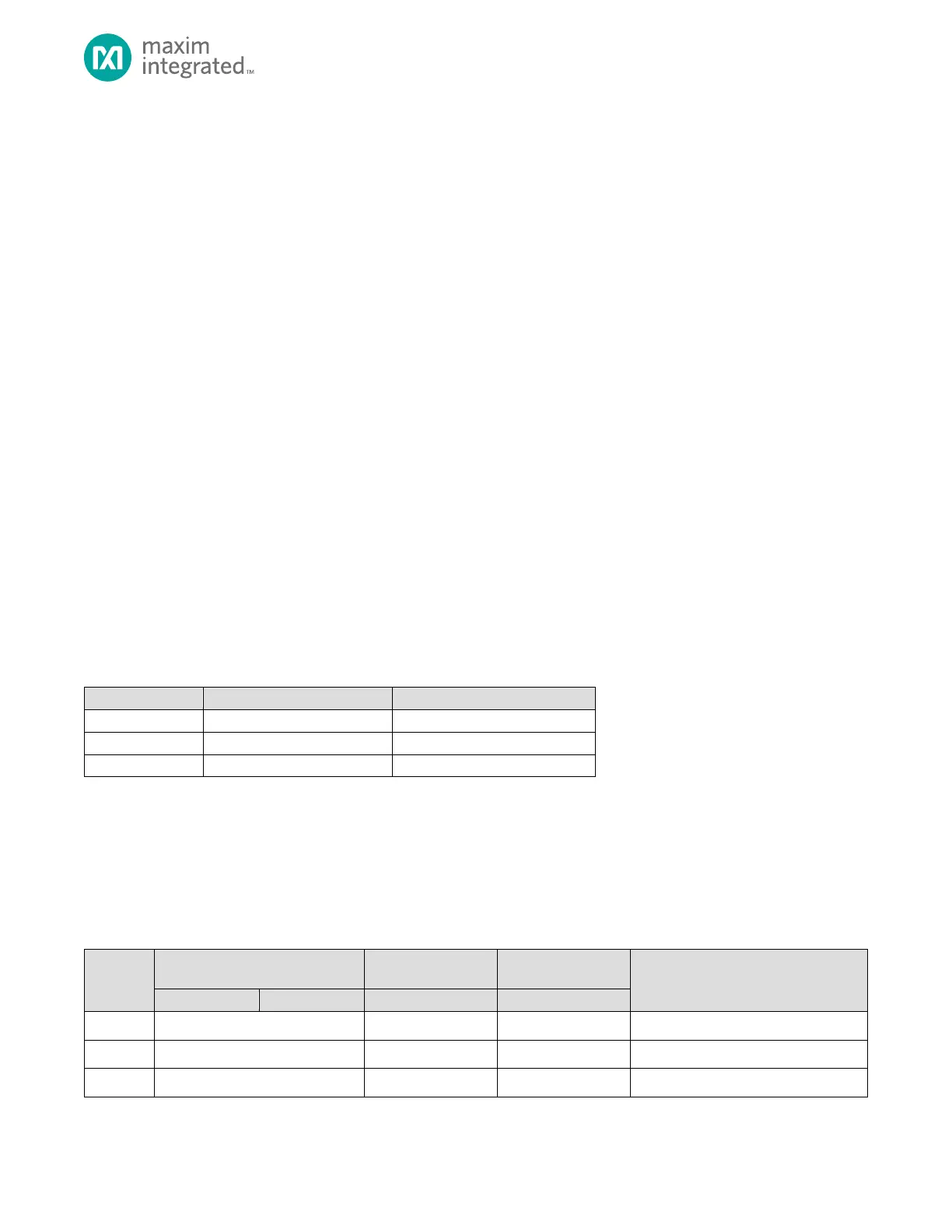

The AHB bus masters are listed in Table 2-2. Each bus slave has a dedicated RPU access control register. Each bit position in

a slave’s RPU register allows or denies access by a specific AHB bus master as shown in in Table 2-2. Register bits

corresponding to unimplemented bus masters should not be changed from their reset default value.

Because of the structure of the APB bus, there is only one access control bit. This means that the read and write access

permissions for a particular master must always be the same. Access permissions for read and write can be configured

separately for AHB slaves.

Table 2-2. MAX32665—MAX32668 Master Permission Bits

Loading...

Loading...