MAX32665-MAX32668 User Guide

Maxim Integrated Page 271 of 457

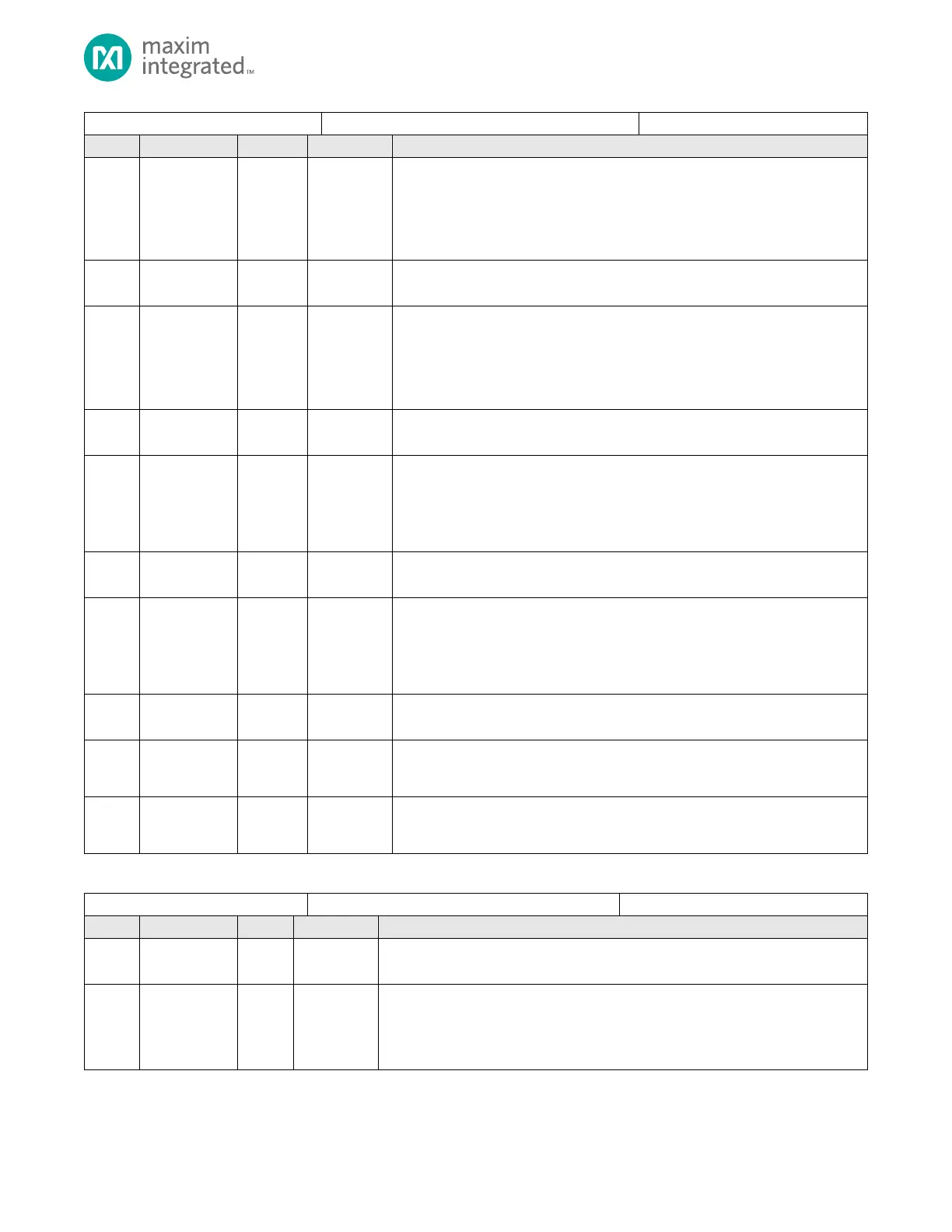

UART DMA Configuration Register

Receive FIFO Level DMA Trigger

If the Receive FIFO level is greater than this value, the DMA channel transfers

data from the Receive FIFO. DMA transfers continue until the Receive FIFO is

empty. To avoid an Receive FIFO overrun, do not set this value to 32.

Values above 32 are reserved for future use.

Reserved for Future Use

Do not modify this field.

Transmit FIFO Level DMA Trigger

If the Transmit FIFO level is less than this value, the DMA channel transfers data

into the Transmit FIFO. DMA transfers continue until the Transmit FIFO is full. To

avoid stalling a UART transmission, do not set this value to 1 or 0.

Note: Values above 32 are Reserved for Future Use.

Reserved for Future Use

Do not modify this field.

Receive DMA Timeout Start

If UARTn_CTRL0.to_cnt causes an RX timeout and UARTn_STAT.rx_num is greater

than zero, the DMA transfer will start. Auto-clear after set.

0: Start not initiated.

1: Start DMA transfer.

Reserved for Future Use

Do not modify this field.

Receive DMA Start

Regardless of the setting of UARTn_DMA.rxdma_lvl, start the DMA transfer if

UARTn_STAT.rx_num is greater than zero. Auto-clear after set.

0: Start not initiated.

1: Start DMA transfer.

Reserved for Future Use

Do not modify this field.

Receive FIFO DMA Channel Enable

0: Disabled.

1: Enabled.

Transmit FIFO DMA Channel Enable

0: Disabled.

1: Enabled.

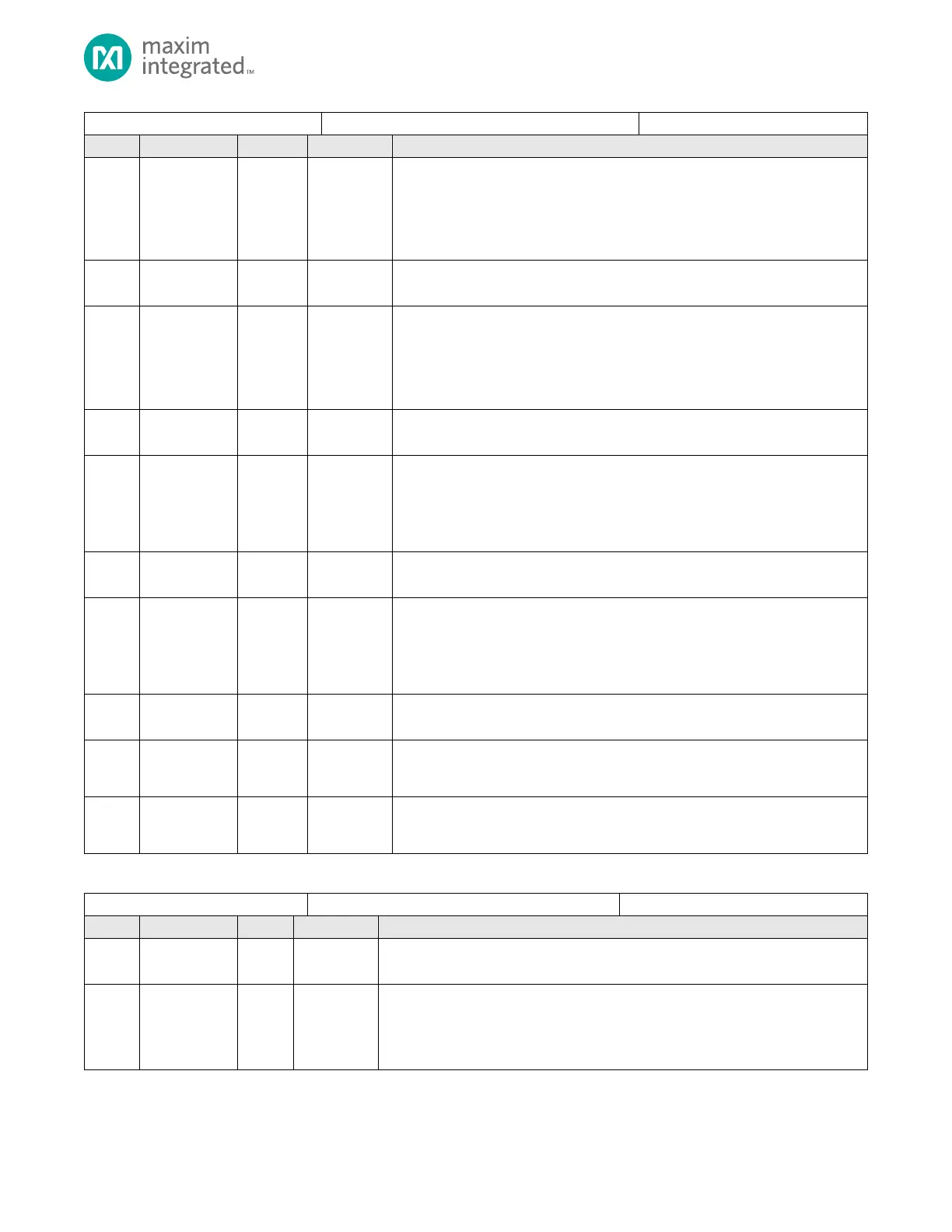

Table 12-13: UART Transmit FIFO Data Output Register

UART Transmit FIFO Register

Reserved for Future Use

Do not modify this field.

Transmit FIFO Peek Register

Reads from this register return the next character available for transmission at the

end of the Transmit FIFO. If no data is available, reads of this field return 0.

Reads from this register do not affect the Transmit FIFO state.

Loading...

Loading...