MAX32665-MAX32668 User Guide

Maxim Integrated Page 409 of 457

Isochronous OUT Endpoint Option

Error Handling – High Bandwidth

Isochronous OUT Endpoints Only

High-bandwidth Isochronous OUT endpoints can transfer three 1024-byte packets in one payload.

To the USB bus, it appears to be a single packet of 3072 bytes. If a high-bandwidth isochronous

data transmission is split into more than one packet, but if less than the expected number of

packets is received by the OUT endpoint, an error condition exists. In this case, the Incomplete

Isochronous Packet Received Error Status bit USBHS_OUTCSRU.incomprx is automatically set to

indicate that the data received in the OUT FIFO is incomplete.

If a packet of the wrong data type is received during a high-bandwidth Isochronous OUT

transaction, then the PID Error Status bit USBHS_OUTCSRU.piderror is automatically set.

21.11 USBHS Device Registers

See Table 3-1: APB Peripheral Base Address Map for the USBHS Peripheral Base Address.

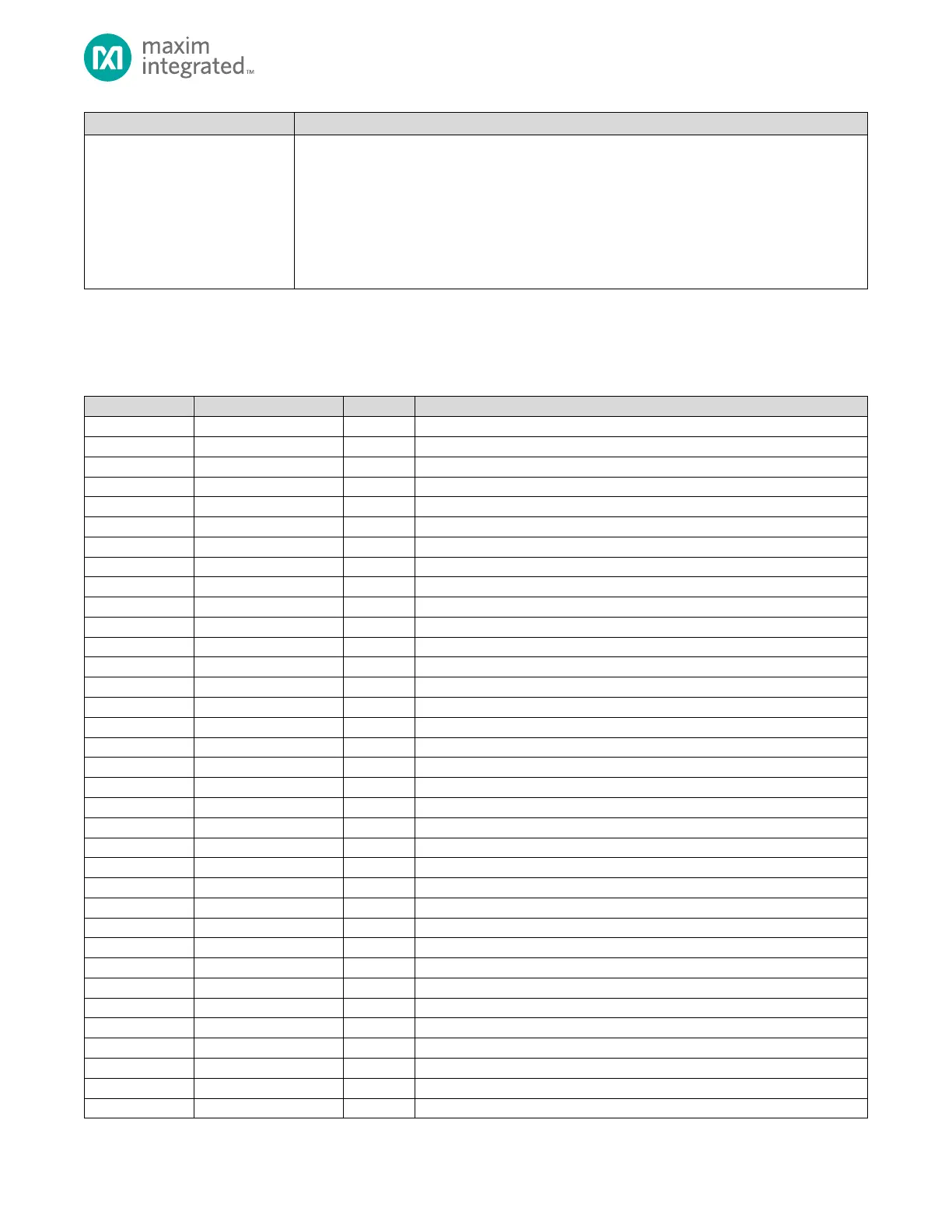

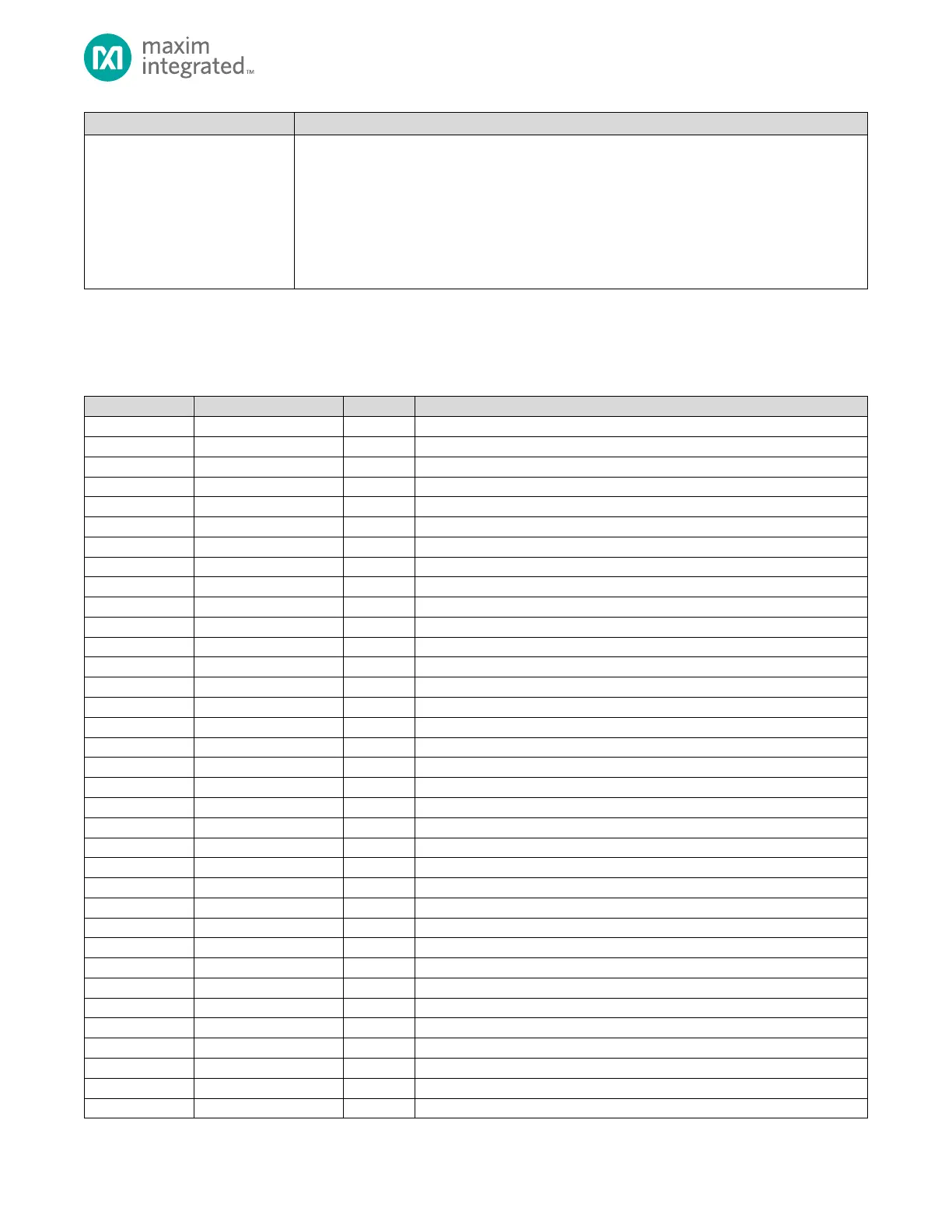

Table 21-5: USBHS Device Register Offsets, Names, Access, and Descriptions

USBHS Device Address Register

USBHS Power Management Register

USBHS IN Endpoint Interrupt Status Register

USBHS OUT Endpoint Interrupt Status Flags Register

USBHS IN Endpoint Interrupt Enable Register

USBHS OUT Endpoint Interrupt Enable Register

USBHS Signaling Interrupt Status Flags Register

USBHS Signaling Interrupt Enable Register

USBHS Frame Number Register

USBHS Endpoint and Status Register Index Register

USBHS IN Endpoint Maximum Packet Size Register

USBHS Endpoint 0 Control Status Register (USBHS_INDEX = 0)

USBHS IN Endpoint Lower Control and Status Register (USBHS_INDEX != 0)

USBHS IN Endpoint Upper Control and Status Register

USBHS OUT Endpoint Maximum Packet Sizes Register

USBHS OUT Endpoint Lower Control Status Register

USBHS OUT Endpoint Upper Control Status Register

USBHS Endpoint 0 IN FIFO Byte Count Register

USBHS Endpoint OUT FIFO Byte Count Register

USBHS FIFO for Endpoint 0 Register

USBHS FIFO for Endpoint 1 Register

USBHS FIFO for Endpoint 2 Register

USBHS FIFO for Endpoint 3 Register

USB HS FIFO for Endpoint 4 Register

USBHS FIFO for Endpoint 5 Register

USBHS FIFO for Endpoint 6 Register

USBHS FIFO for Endpoint 7 Register

USBHS FIFO for Endpoint 8 Register

USBHS FIFO for Endpoint 9 Register

USBHS FIFO for Endpoint 10 Register

USBHS FIFO for Endpoint 11 Register

USBHS Endpoint Count Info Register

USBHS RAM and MAInfo Register

USBHS Soft Reset Control Register

Loading...

Loading...