MAX32665-MAX32668 User Guide

Maxim Integrated Page 48 of 457

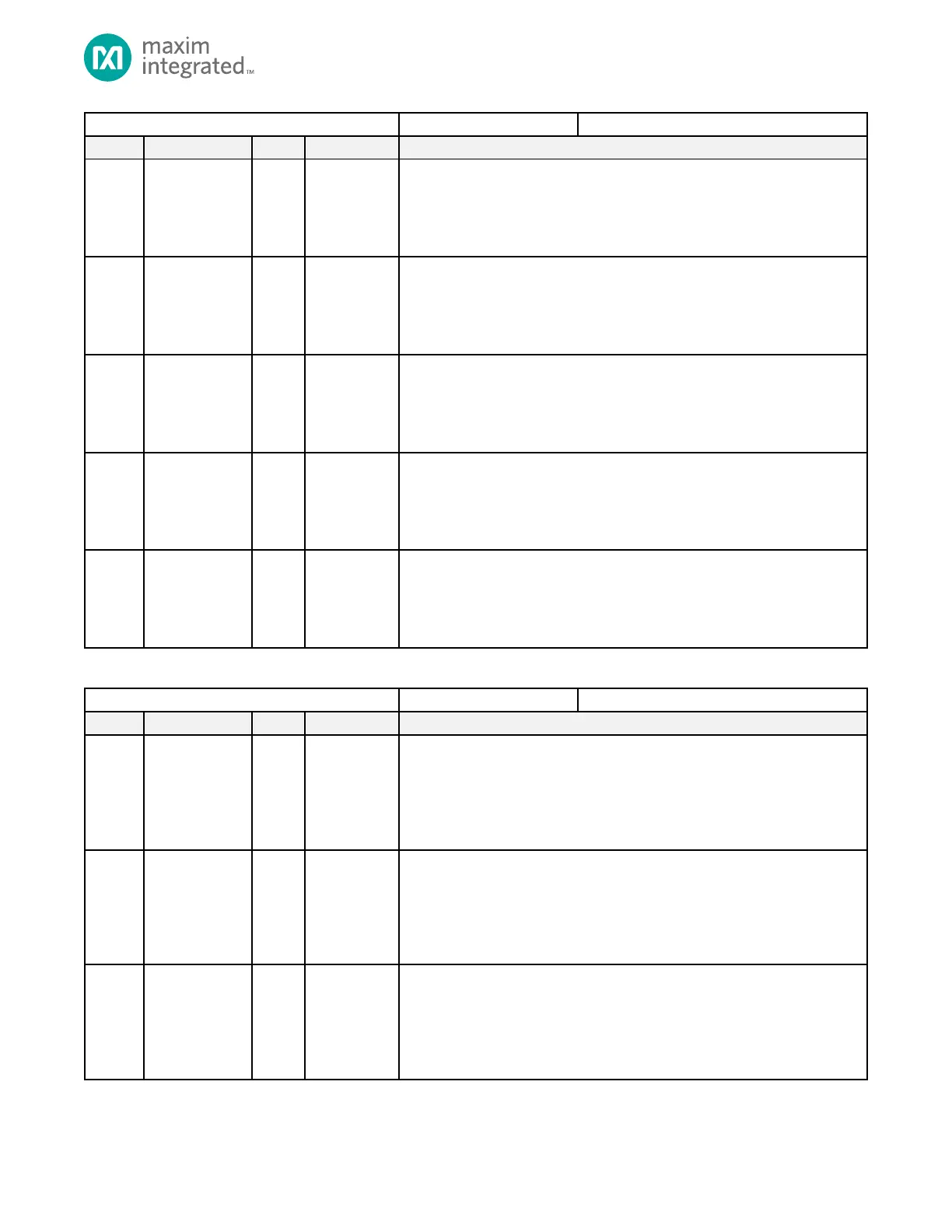

Error Correction Coding Interrupt Enable

ECC Sysram4 Interrupt Enable

When set, indicates that the interrupt is enabled for occurrence upon a

detected error in the Sysram4 block if GCR_ECC_EN.sysram4en is set.

0: Disabled

1: Enabled

ECC Sysram3 Interrupt Enable

When set, indicates that the interrupt is enabled for occurrence upon a

detected error in the Sysram3 block and GCR_ECC_EN.sysram3en is set.

0: Disabled

1: Enabled

ECC Sysram2 Interrupt Enable

When set, indicates that the interrupt is enabled for occurrence upon a

detected error in the Sysram2 block and GCR_ECC_EN.sysram2en is set.

0: Disabled

1: Enabled

ECC Sysram1 Interrupt Enable

When set, indicates that the interrupt is enabled for occurrence upon a

detected error in the Sysram1 block and GCR_ECC_EN.sysram1en is set.

0: Disabled

1: Enabled

ECC Sysram0 Interrupt Enable

When set, indicates that the interrupt is enabled for occurrence upon a

detected error in the Sysram0 block and GCR_ECC_EN.sysram0en is set.

0: Disabled

1: Enabled

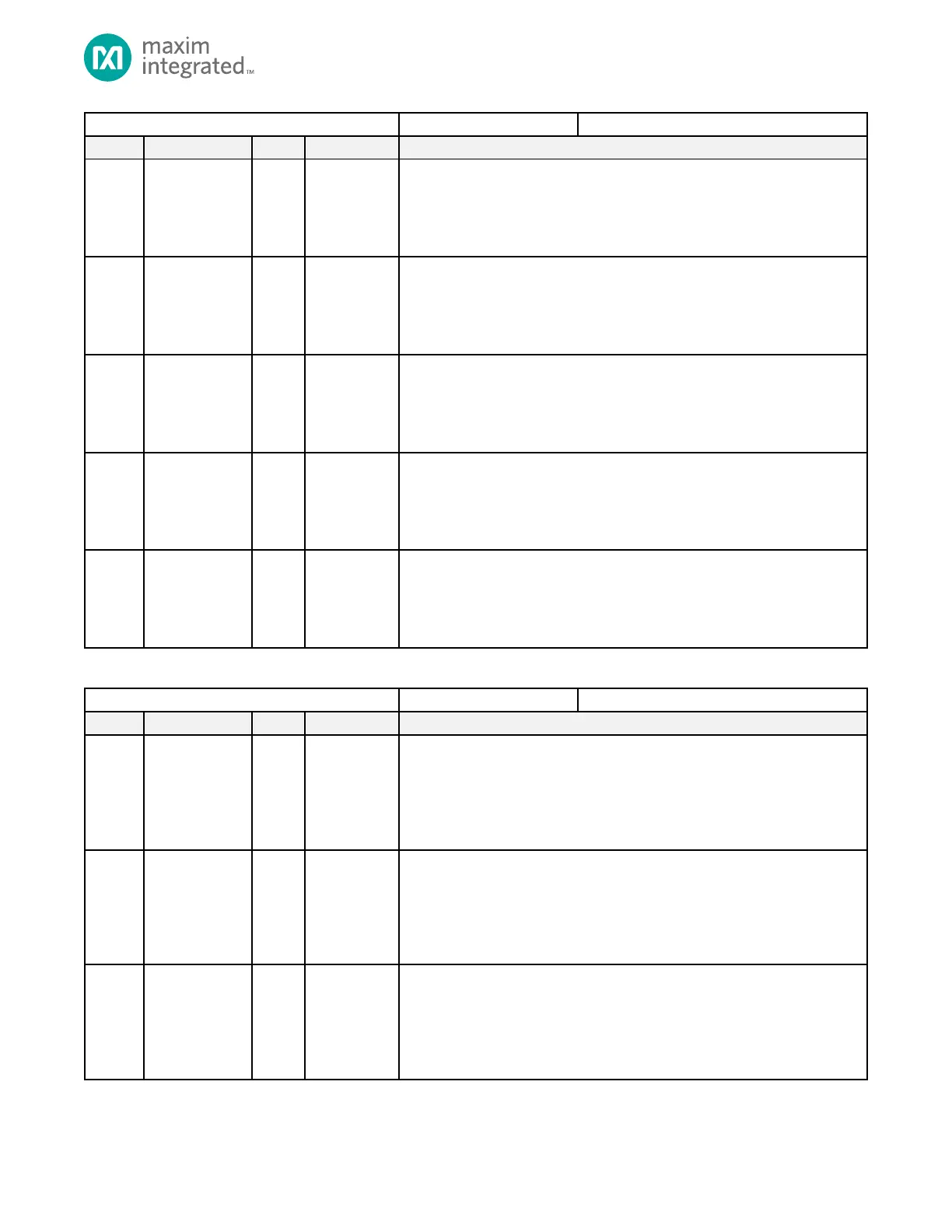

Table 3-7: Error Correction Coding (ECC) Address Register

Error Correction Coding Address

ECC Error Address/TAG RAM Error

Data depends on which block has reported the error. If sysram, fl0, or fl1, then

this bit(s) represents bit 31 of the AMBA address of read which produced the

error. If the error is from one of the caches, then this bit is set as shown below:

0: No Error

1: Tag_Error. The error is in the TAG RAM

ECC Error Address/TAG RAM Error Bank

Data depends on which block has reported the error. If sysram, fl0, or fl1, then

this bit(s) represents bit 30 of the AMBA address of read which produced the

error. If the error is from one of the caches, then this bit is set as shown below:

0: Error is in TAG RAM Bank 0

1: Error is in TAG RAM Bank 1

ECC Error Address/TAG RAM Error Address

Data depends on which block has reported the error. If sysram, fl0, or fl1, then

this bit(s) represents bits 29:16 of the AMBA address of read which produced

the error. If the error is from one of the caches, then this bit is set as shown

below:

[TAG ADDRESS]: Represents the TAG RAM Address

Loading...

Loading...