MAX32665-MAX32668 User Guide

Maxim Integrated Page 300 of 457

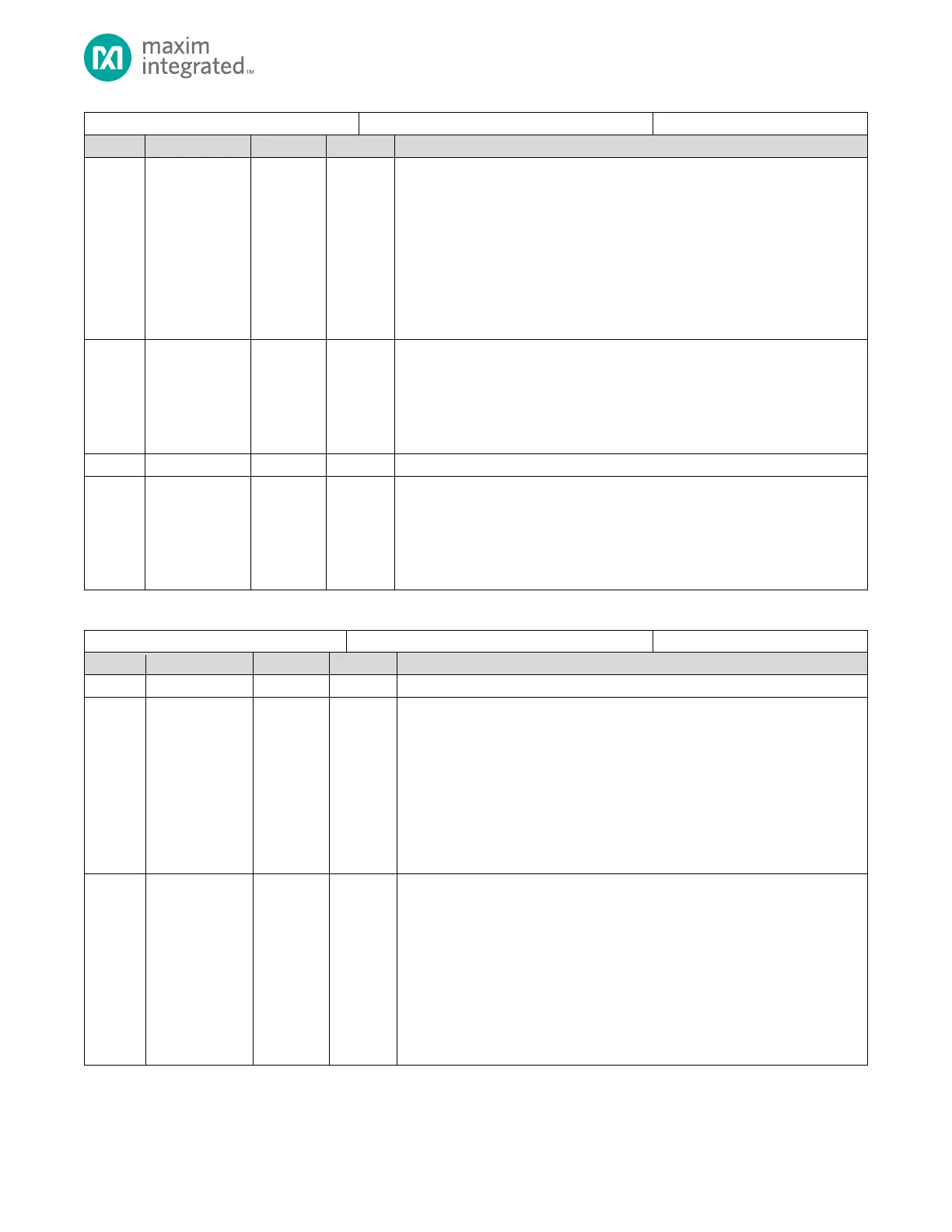

RX FIFO Threshold Level

Set this field to the required number of bytes to trigger a RX FIFO threshold

event. When the number of bytes in the RX FIFO is equal to or greater than this

field, the hardware sets the I2Cn_INT_FL0.rxthi bit indicating an RX FIFO

threshold level event.

0: 0 bytes or more in the RX FIFO causes a threshold event.

1: 1+ bytes in the RX FIFO triggers a receive threshold event (recommended

minimum value).

…

8: RX FIFO threshold event only occurs when the RX FIFO is full.

Flush RX FIFO

Write 1 to this field to initiate a RX FIFO flush, clearing all data in the RX FIFO.

This field is automatically cleared by hardware when the RX FIFO flush completes.

Writing 0 has no effect.

0: RX FIFO flush complete or not active.

1: Flush the RX FIFO

Slave Mode Do Not Respond

Slave mode operation only. If the device has been addressed for a write

operation, and there is still data in the RX_FIFO then:

0: Always respond to an address match with an ACK but then always respond

to data bytes with a NACK.

1: NACK the address.

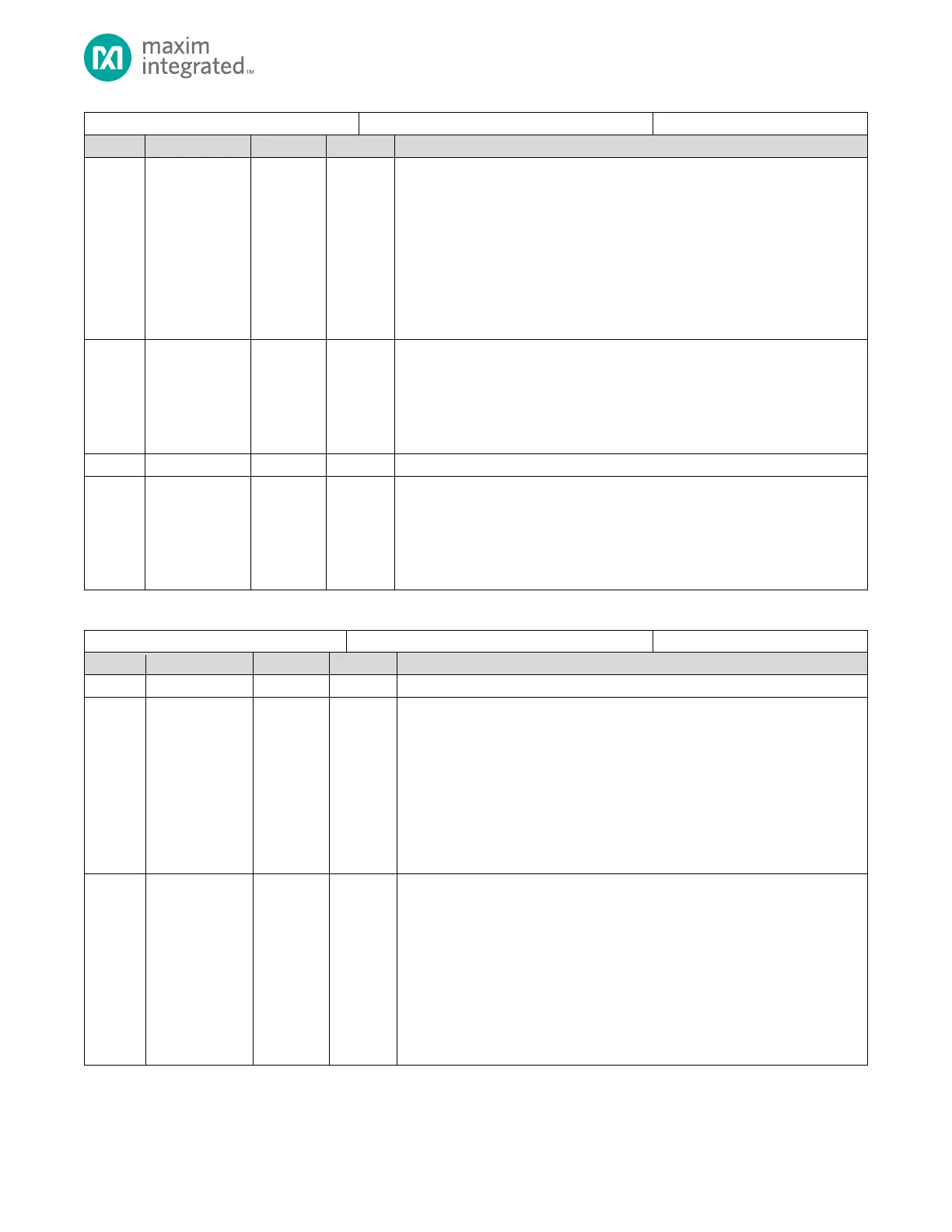

Table 13-14: I

2

C Receive Control 1 Register

RX FIFO Byte Count Status

0: No data in the RX FIFO.

1: 1 byte in the RX FIFO.

2: 2 bytes in the RX FIFO.

3: 3 bytes in the RX FIFO.

4: 4 bytes in the RX FIFO.

5: 5 bytes in the RX FIFO.

6: 6 bytes in the RX FIFO.

7: 7 bytes in the RX FIFO.

8: 8 bytes in the RX FIFO (max value).

RX FIFO Transaction Byte Count Configuration

When in Master Mode, write the number of bytes to be received in a transaction

from 1 to 256. 0x00 represents 256.

0: 256 byte receive transaction.

1: 1 byte receive transaction.

2: 2 byte receive transaction.

…

255: 255 byte receive transaction.

This field is ignored when I2Cn_CTRL0.irxm = 1. To receive more than 256 bytes,

use I2Cn_CTRL0.irxm = 1

Loading...

Loading...