MAX32665-MAX32668 User Guide

Maxim Integrated Page 444 of 457

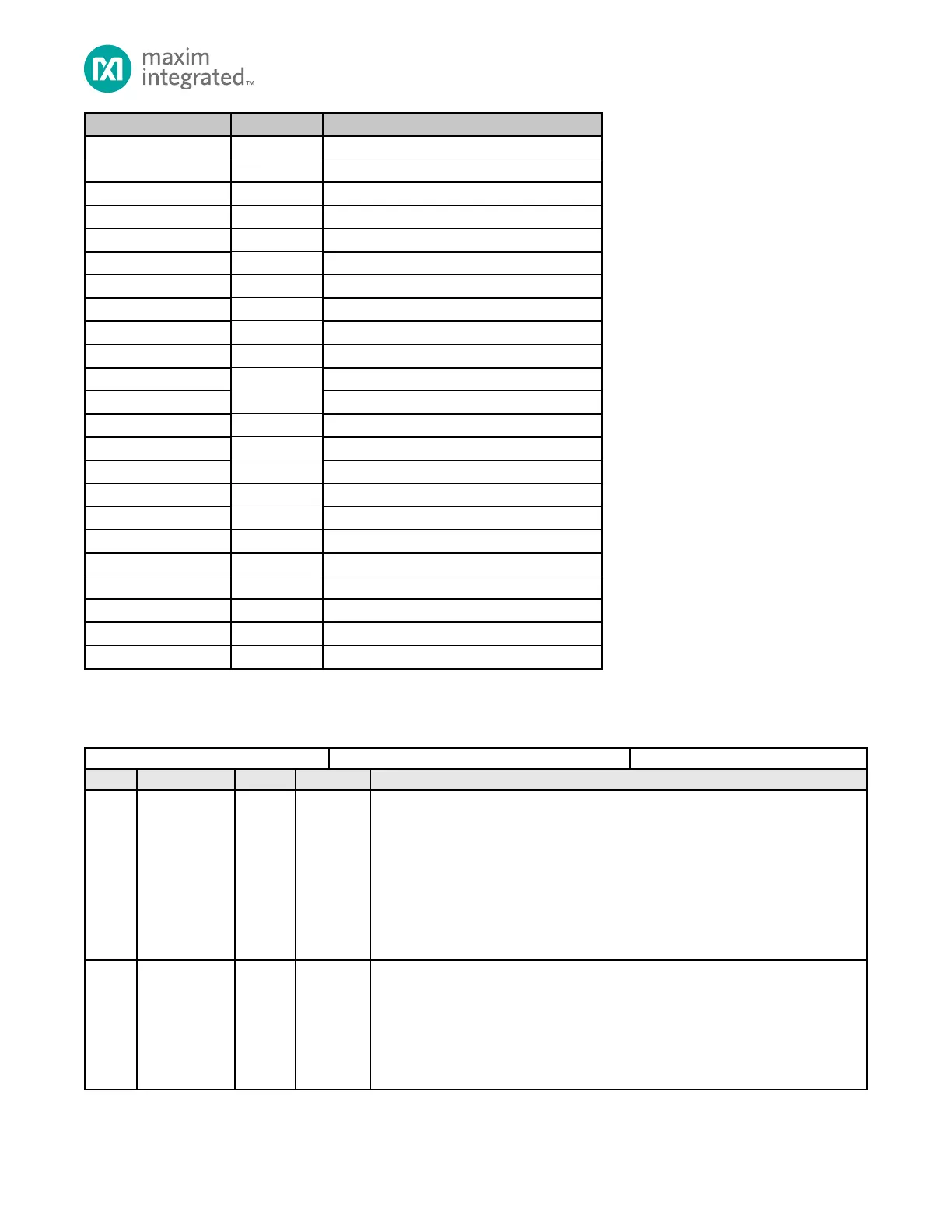

Hash Message Digest [31:0]

Hash Message Digest [63:32]

Hash Message Digest [95:64]

Hash Message Digest [127:96]

Hash Message Digest [159:128]

Hash Message Digest [191:160]

Hash Message Digest [223:192]

Hash Message Digest [255:224]

Hash Message Digest [287:256]

Hash Message Digest [319:288]

Hash Message Digest [351:320]

Hash Message Digest [383:352]

Hash Message Digest [415:384]

Hash Message Digest [447:416]

Hash Message Digest [479:448]

Hash Message Digest [511:480]

Hash Message Size [63:32]

Hash Message Size [95:64]

Hash Message Size [127:96]

23.9 Register Details

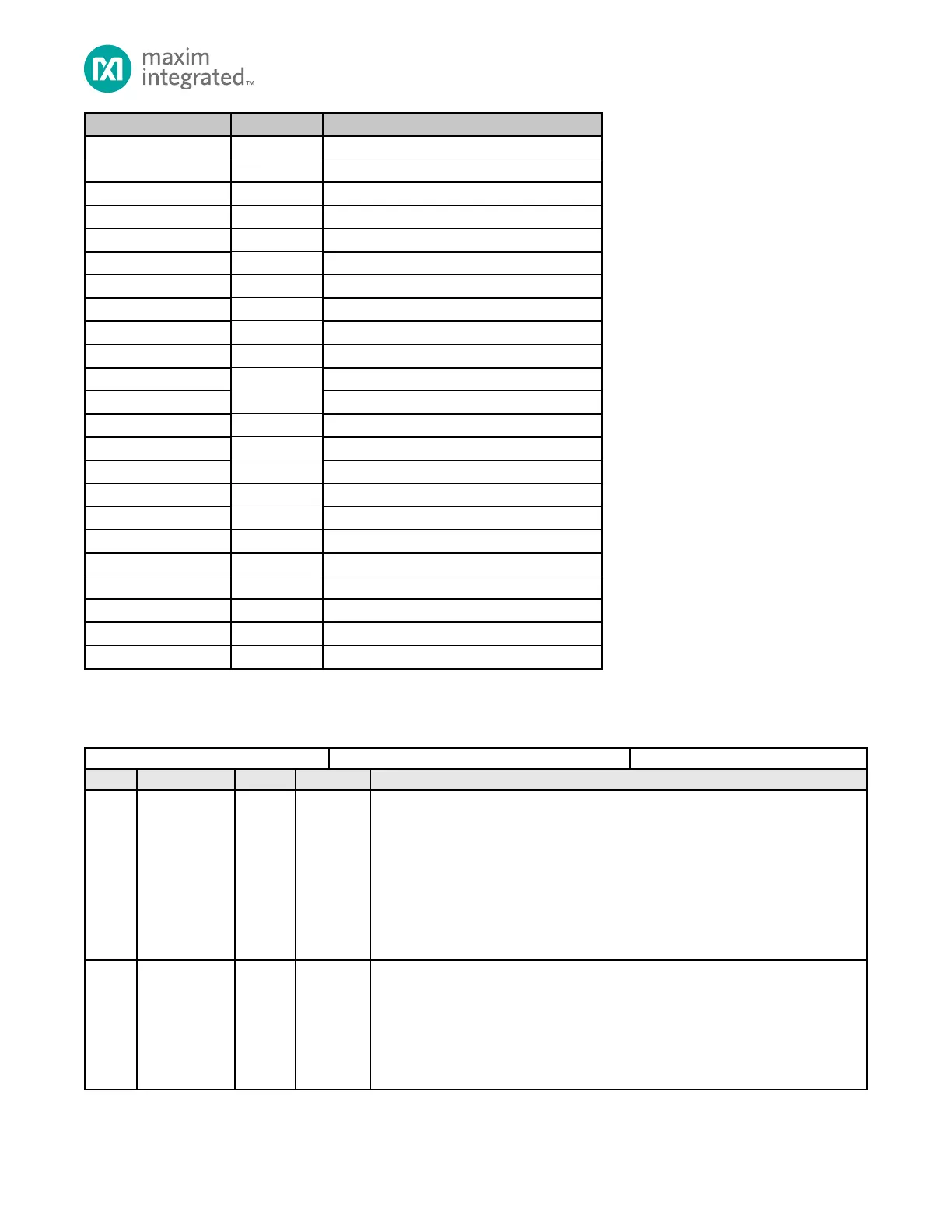

Table 23-8: Cryptographic Control Register

Cryptographic Control Register

Cryptographic Operation Done

This bit is set whenever hardware completes an MMA, cipher or hash operation and

sets the corresponding “done” bit in CRYPTO_CTRL.[27:25]. This bit remains set until

cleared by software. Writing 0 to one or more of the bits in CRYPTO_CTRL.[27:24] will

not effect this bit.

Setting the CRYPTO_CTRL.dmanemsk bit to 1 will cause this bit to be set to 1 when

hardware sets the CRYPTO_CTRL.dma_done bit.

0: No cryptographic operations have completed since this bit was cleared.

1: One or more cryptographic operations are complete.

Cryptographic Block Ready

Hardware clears this status bit to 0 when software initiates a reset of the

cryptographic accelerator by setting the CRYPTO_CTRL.rst.bit. Software must poll this

bit until it is set to 1 by hardware, indicating cryptographic accelerator is again ready

for use.

0: Cryptographic accelerator reset in progress.

1: Cryptographic accelerator ready for use

Loading...

Loading...