MAX32665-MAX32668 User Guide

Maxim Integrated Page 112 of 457

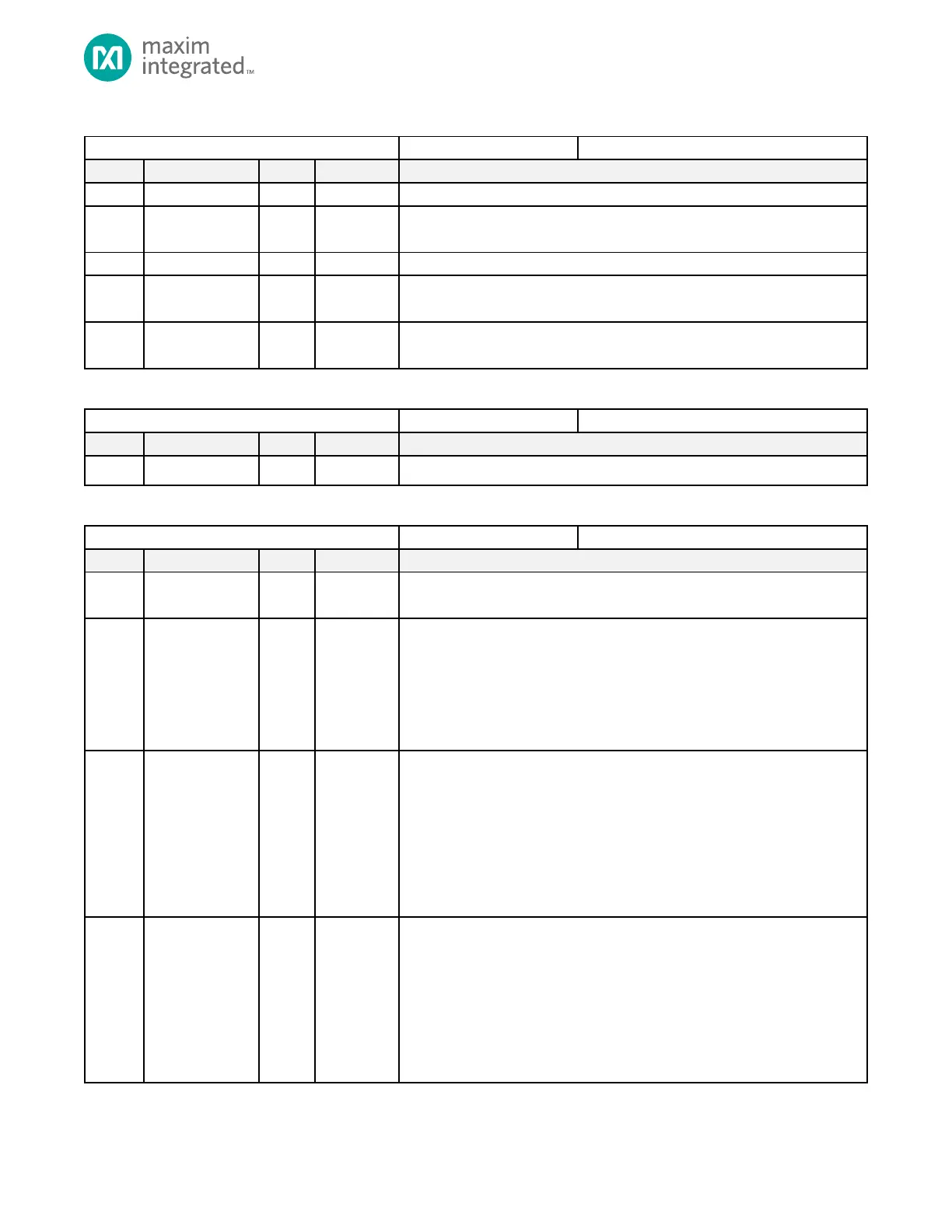

Table 4-73: Bluetooth LDO Delay Count Register

Bluetooth LDO Delay Count

Bluetooth LDOTX Delay Count

Not used.

Bluetooth LDORX Delay Count

Not used.

Bluetooth LDO Bypass Delay Count

Not used.

Table 4-74: General Purpose 0 Register

User-defined register RAM

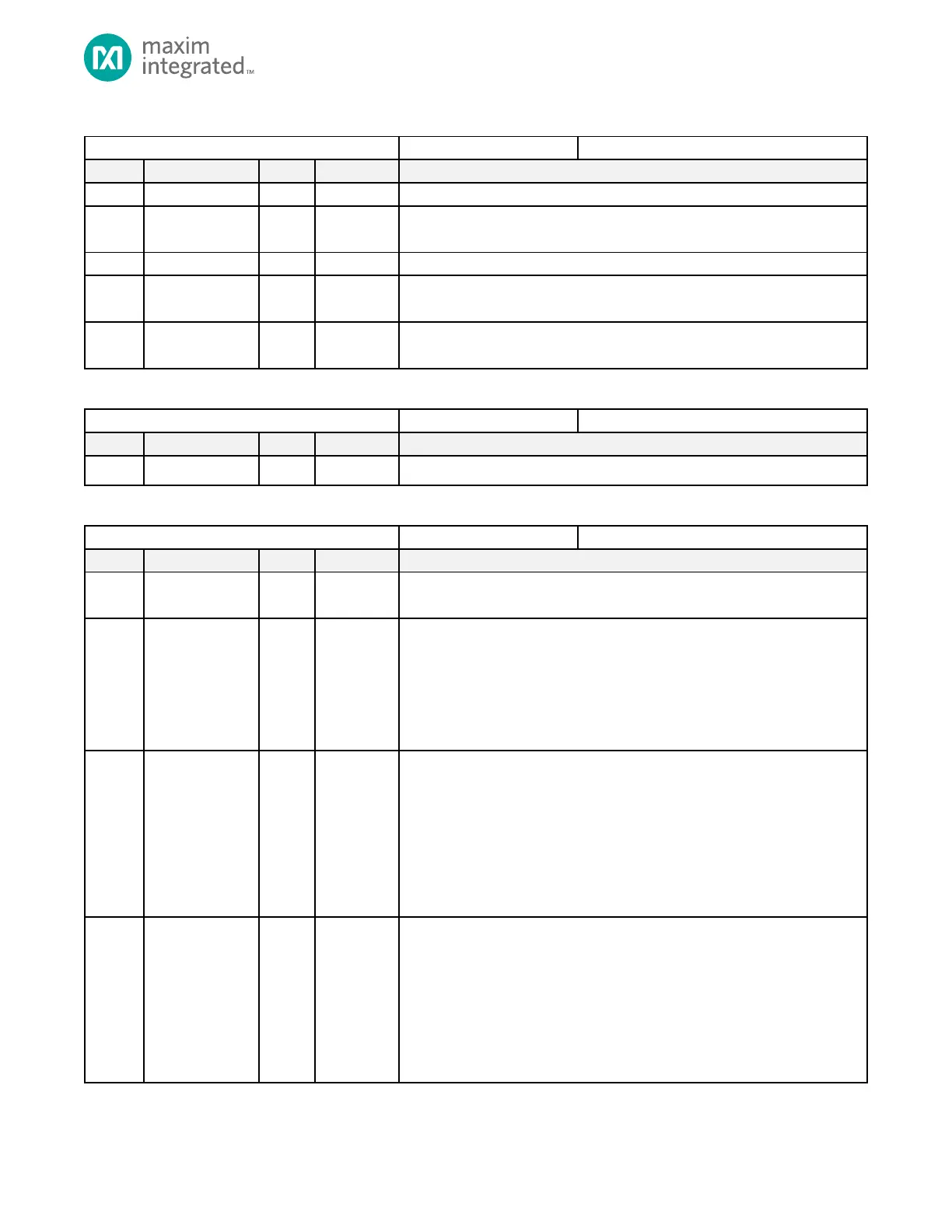

Table 4-75: Arm Peripheral Bus Asynchronous Bridge Select Register

Arm Peripheral Bus Asynchronous Bridge Select

Reserved

Do not modify this field.

Pulse Trains Peripheral Bus Select

This peripheral can be connected to the APB PCLK domain or a 7.3728MHz bus

can be used. It takes 3 cycles of the 7.3728MHz clock to switch PCLK or 3 cycles

of the PCLK clock to switch to 7.37MHz clock. After switching, ensure enough

time before accessing the peripheral registers.

0: Peripheral is accessed on the PCLK bus.

1: Peripheral is accessed on the 7.3728MHz bus.

I2C2 Peripheral Bus Select

The access for this peripheral can be performed via one of two different

peripheral bus configurations. The system PCLK can be used as any of the other

system peripherals that are connected to the APB PCLK domain or a 7.3728MHz

bus can be used. It takes 3 cycles of the 7.3728MHz clock to switch PCLK or 3

cycles of the PCLK clock to switch to 7.37MHz clock. After switching, ensure

enough time before accessing the peripheral registers.

0: PCLK bus selected

1: 7.3728MHz bus selected

I2C1 Peripheral Bus Select

The access for this peripheral can be performed via one of two different

peripheral bus configurations. The system PCLK can be used as any of the other

system peripherals that are connected to the APB PCLK domain or a 7.3728MHz

bus can be used. It takes 3 cycles of the 7.3728MHz clock to switch PCLK or 3

cycles of the PCLK clock to switch to 7.37MHz clock. After switching, ensure

enough time before accessing the peripheral registers.

0: PCLK bus selected

1: 7.3728MHz bus selected

Loading...

Loading...