MAX32665-MAX32668 User Guide

Maxim Integrated Page 63 of 457

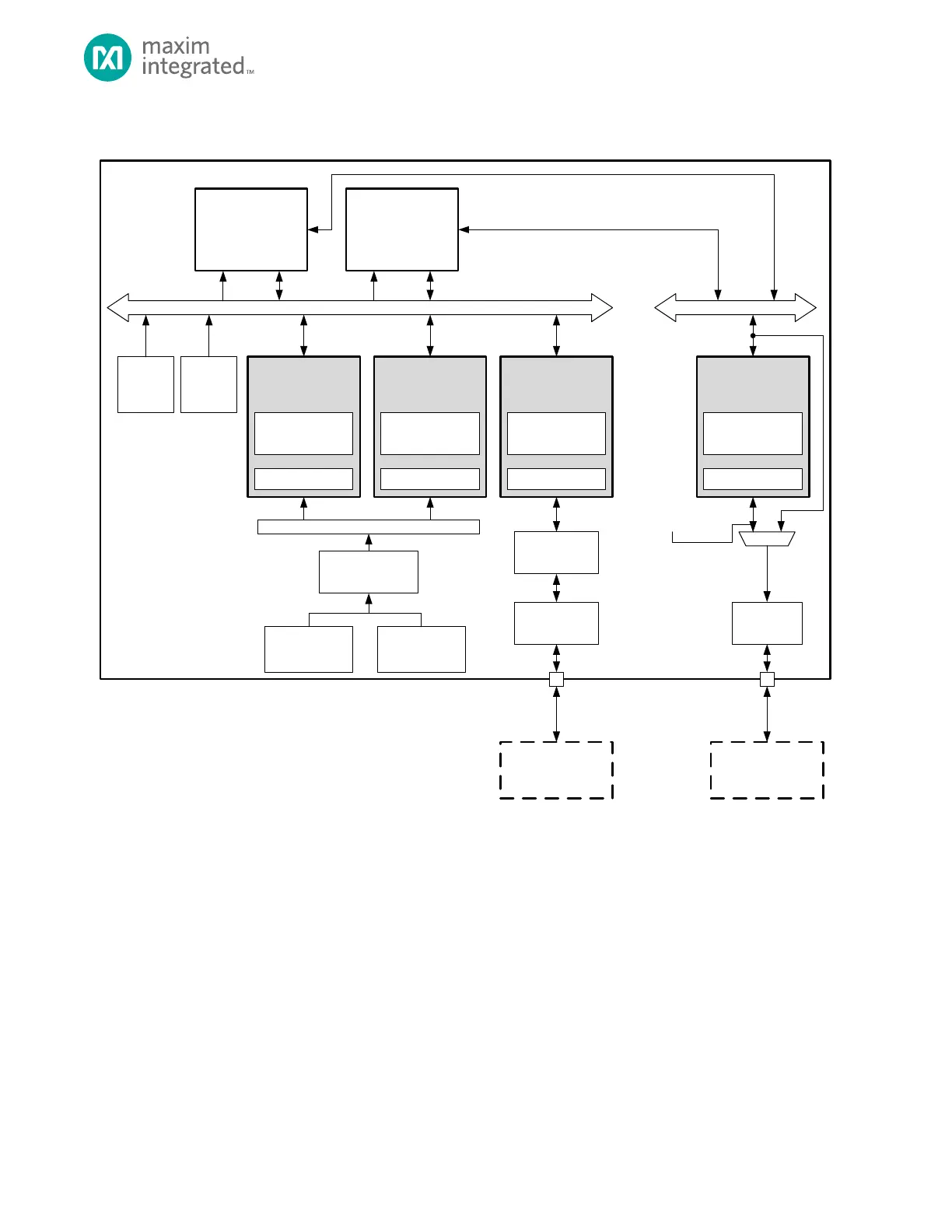

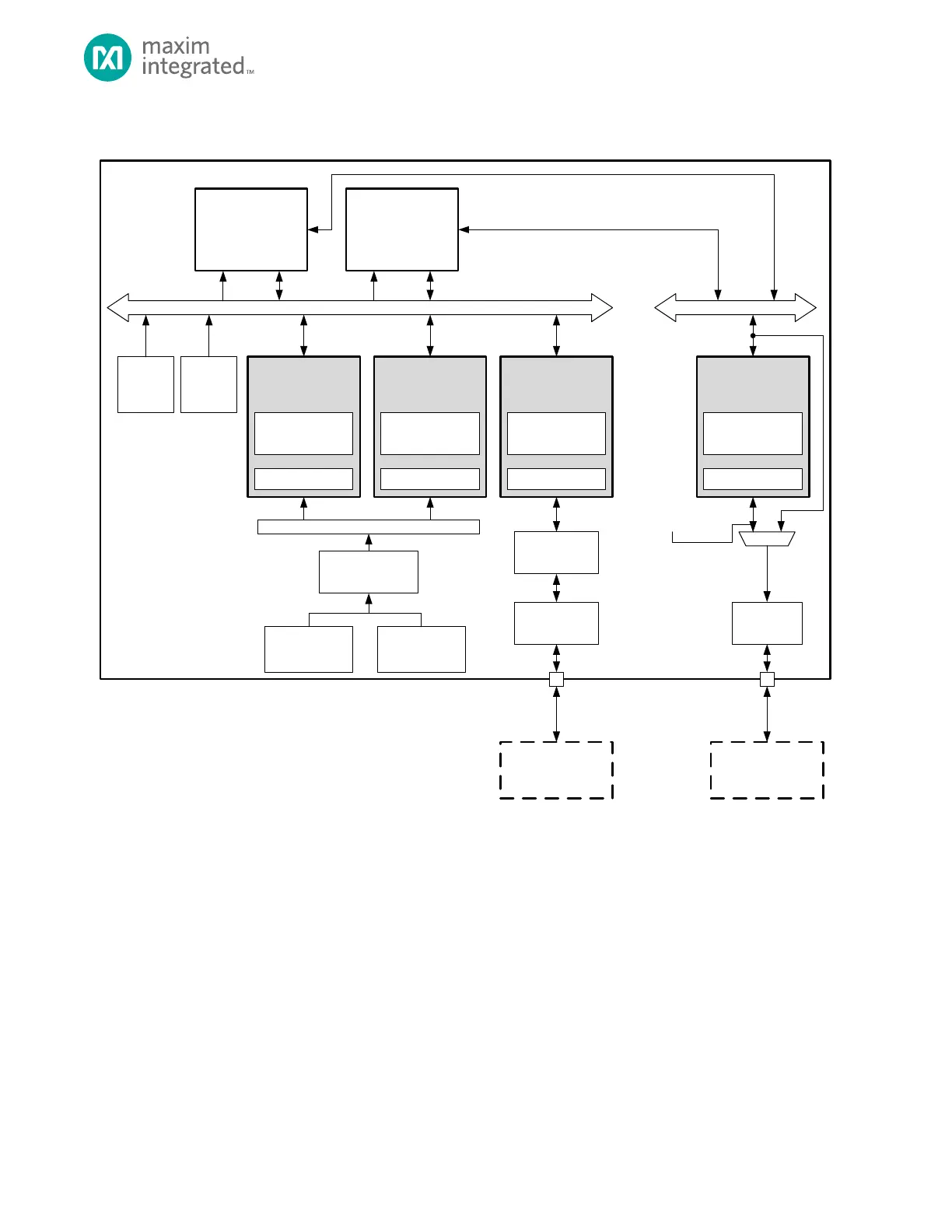

Figure 4-6: MAX32665—MAX32668 Cache Controllers Control

4.5 Instruction Cache Controller

ICC0, ICC1 and SFCC are independent cache controllers and each is controlled directly using their respective register set.

4.5.1 Enabling ICC0/ICC1/SFCC

Perform the following steps to enable ICC0 or ICC1.

1. Set PWRSEQ_LPMEMSD.icachensd to 0 to ensure the cache power is on.

2. Set ICCn_CACHE_CTRL.enable to 1.

3. Read ICCn_CACHE_CTRL.ready until it returns 1.

Loading...

Loading...