MAX32665-MAX32668 User Guide

Maxim Integrated Page 152 of 457

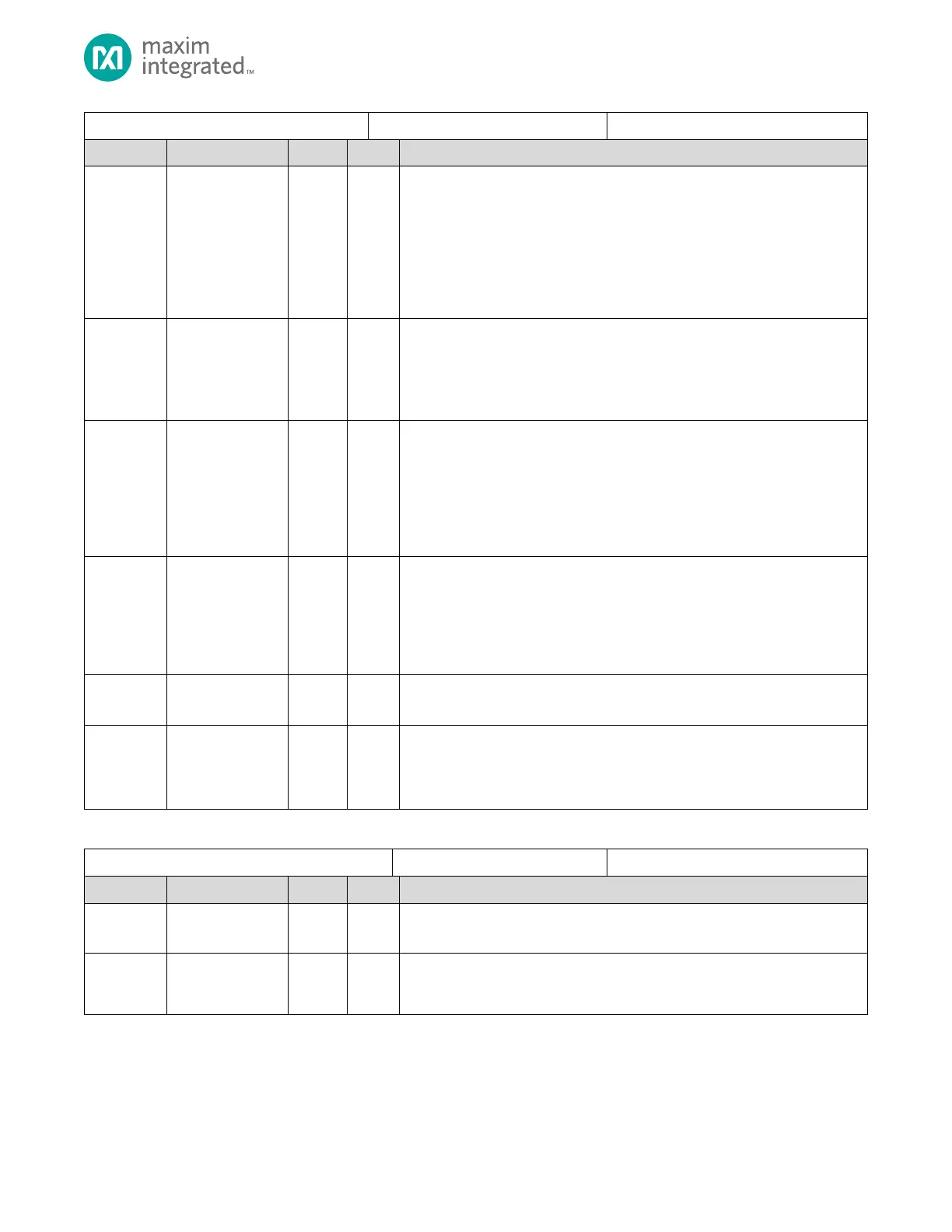

SPIXF Controller Configuration Register

SCK Low Clocks

Number of system clocks that SCK is held low when SCK pulses are generated

0: 16 system clocks

1: 1 system clock

2: 2 system clocks

3: 3 system clocks

All other values: This value defines the number of system clock that SCK is

held low.

SCK High Clocks

Number of system clocks that SCK is held high when SCK pulses are generated.

00: 16 system clocks.

All other values: This value defines the number of system clock that SCK is held

high.

Page Size

Defines the number of bytes per page for transactions that define transfers in

terms of pages.

00: 4 bytes

01: 8 bytes

10: 16 bytes

11: 32 bytes

SPI Mode.

Defines the SPI mode.

00: SPI Mode 0. Clock Polarity = 0, Clock Phase = 0

01: Invalid

10: Invalid

11: SPI Mode 3. Clock Polarity = 1, Clock Phase = 1

Reserved for Future Use

Do not modify this field.

Slave Select.

Only Slave 0 is supported

0b000: Slave 0 is selected

0b001-0b111: Invalid

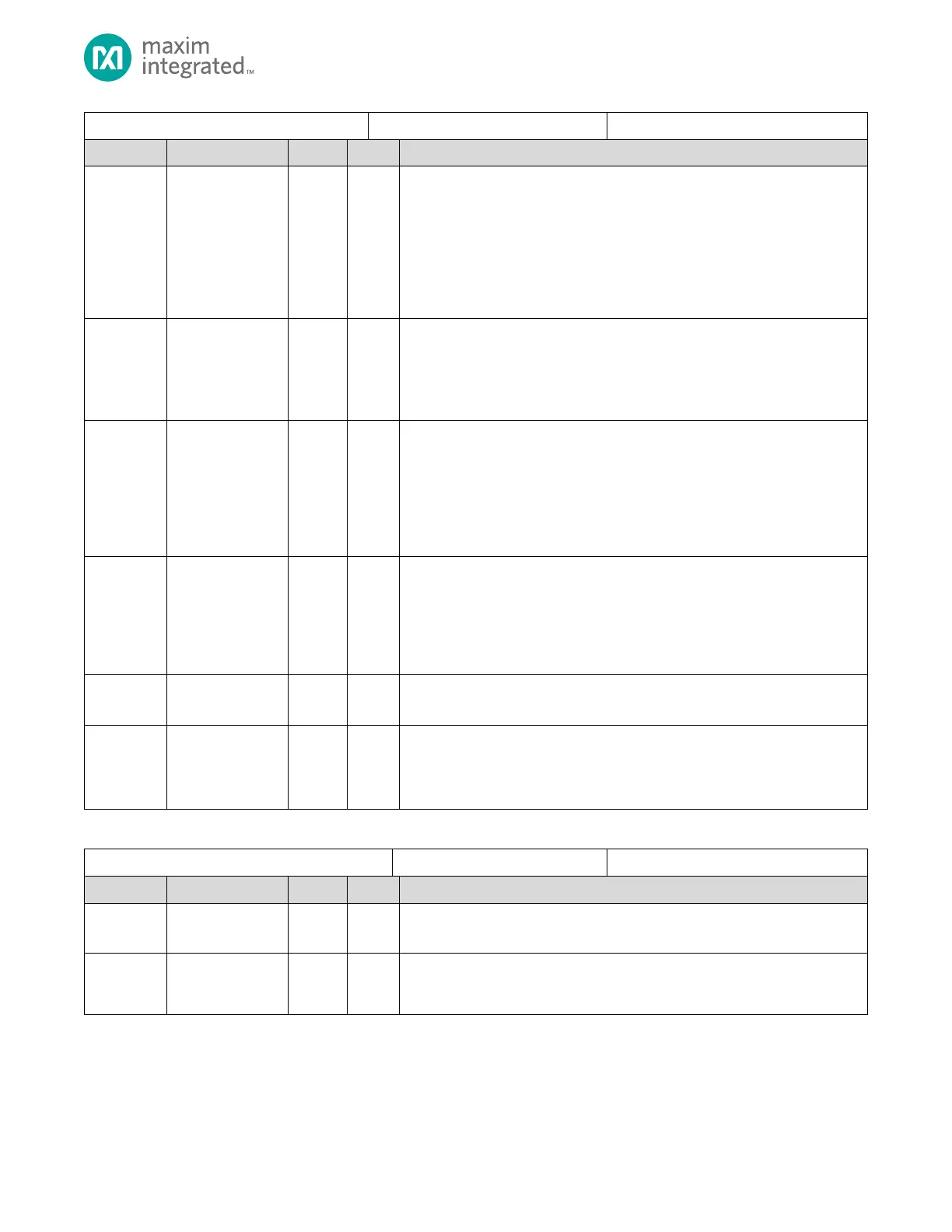

Table 8-6. SPIXF Controller Slave Select Polarity Register

SPIXF Controller Slave Select Polarity Register

Reserved for Future Use

Do not modify this field.

Slave Select 0 Polarity

0: Active Low

1: Active High

Loading...

Loading...