MAX32665-MAX32668 User Guide

Maxim Integrated Page 212 of 457

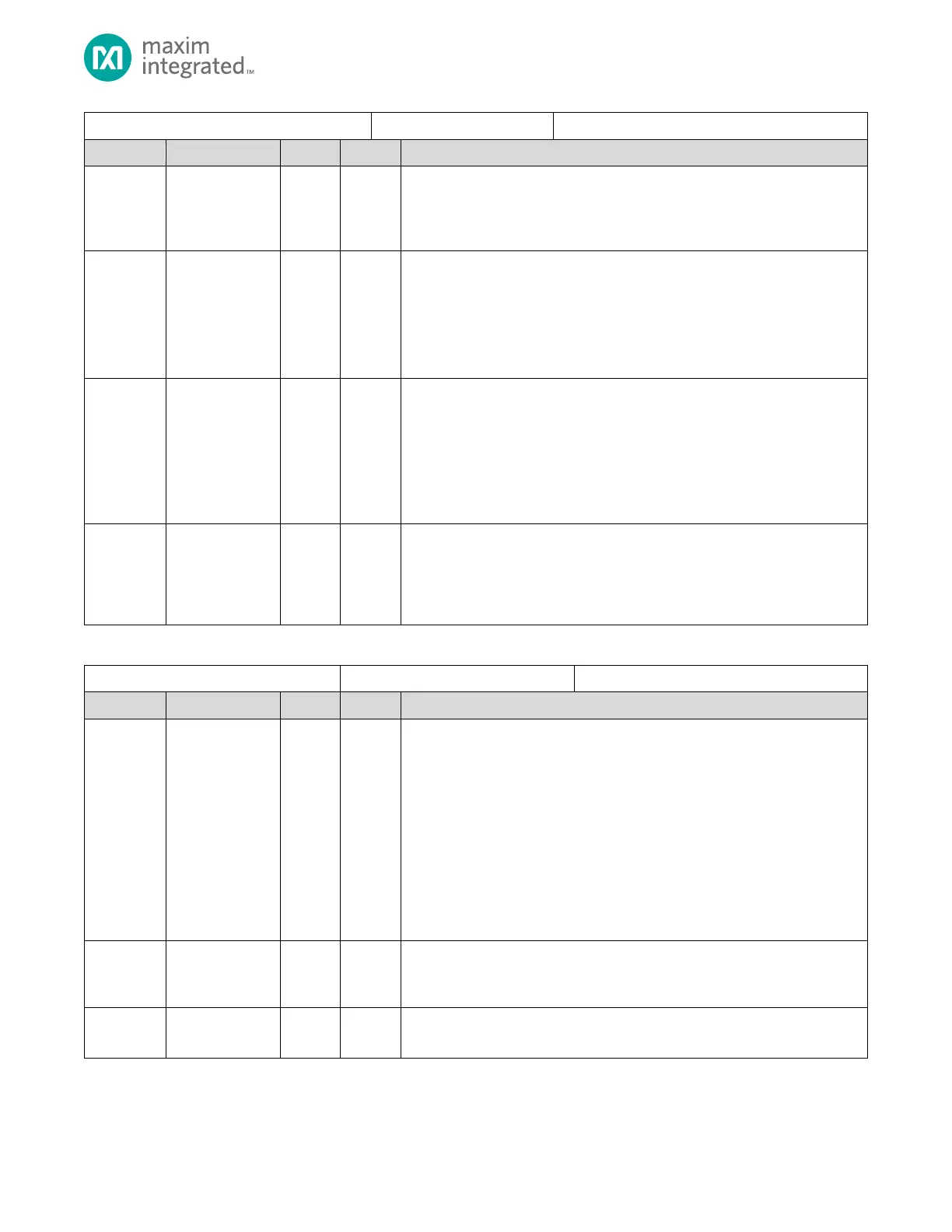

Auto CMD Error Status Register

Auto CMD End Bit Error

Set if the end bit of the Command Response is 0.

1: End Bit Error

0: No Error

Auto CMD CRC Error

Set if CRC error in command response.

1: CRC Error

0: No Error

Note: If both SDHC_AUTO_CMD_ER.crc and SDHC_AUTO_CMD_ER.to are set,

then a CMD-line conflict occurred.

Auto CMD Timeout Error

Set if no response is returned within 64 SDCLK cycles from the end bit of the

command. If set, then ignore bits 4:2 of this register.

1: Timeout Error

0: No Error

Note: If both SDHC_AUTO_CMD_ER.crc and SDHC_AUTO_CMD_ER.to are set,

then a CMD-line conflict occurred.

Auto CMD12 Not Executed Error

Auto CMD12 was not issued to stop a multi-block memory transfer due to an

error with a prior command.

1: Not Executed

0: No Error or error generated by Auto CMD23

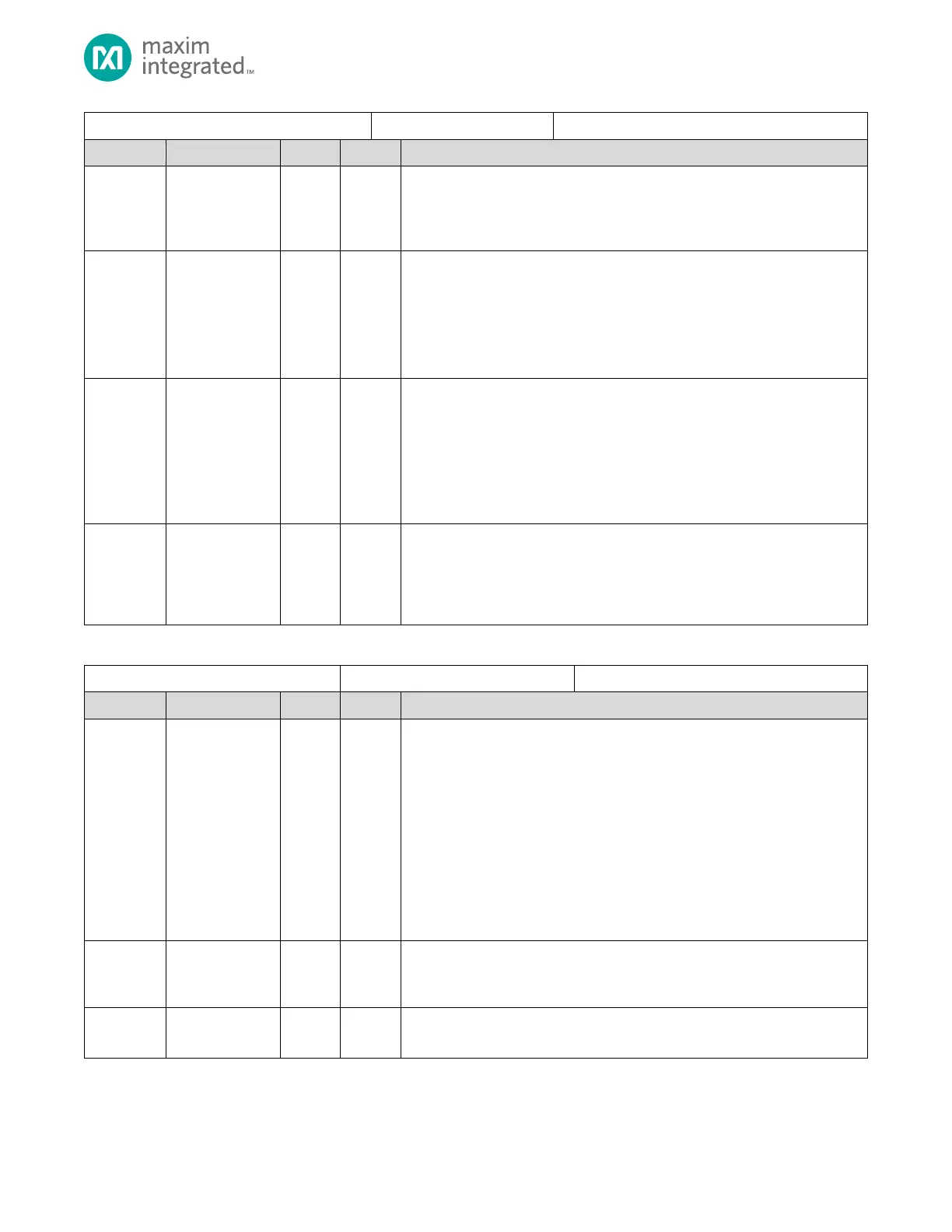

Table 8-82: SDHC Host Control 2 Register

Preset Value Enable

When set to 0, the following fields must be set by the Card Driver:

• SDCLK Frequency Select (SDHC_CLK_CN.sdclk_freq_sel)

• Clock Generator Select (SDHC_CLK_CN.clk_gen_sel)

• Driver Strength Select (SDHC_HOST_CN_2.driver_strength)

If set to 1, the Host Controller hardware sets the above fields based on the

values in the Preset Value registers.

0: Card Driver must set the SDCLK Frequency Select, Clock Generator Select

and Driver Strength Select fields.

1: The Host Controller hardware sets the above fields using the Preset Value

register settings.

Asynchronous Interrupt Enable

Always reads 0. Asynchronous Interrupt Enable is not supported by the

MAX32665—MAX32668. Writes to this field have no effect.

Reserved for Future Use

Do not modify this field.

Loading...

Loading...