MAX32665-MAX32668 User Guide

Maxim Integrated Page 361 of 457

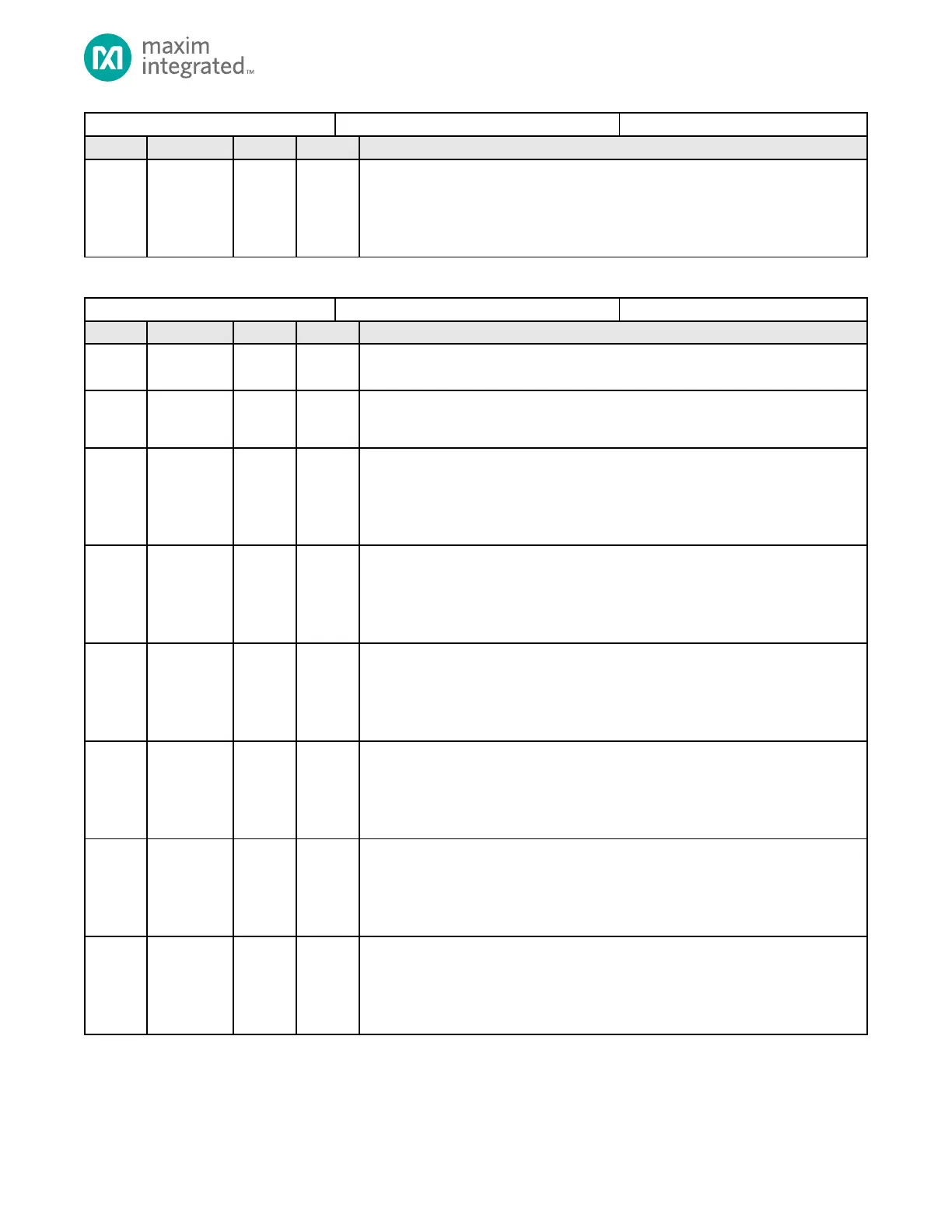

PT Stopped Interrupt Flag Register

PT0 Stopped Status Flag

This bit is set to 1 by hardware when the corresponding pulse train is in Pulse Train

Mode and the loop counter reaches 0. In Square Wave mode, this field is not used.

Write 1 to clear.

1: Pulse Train is stopped.

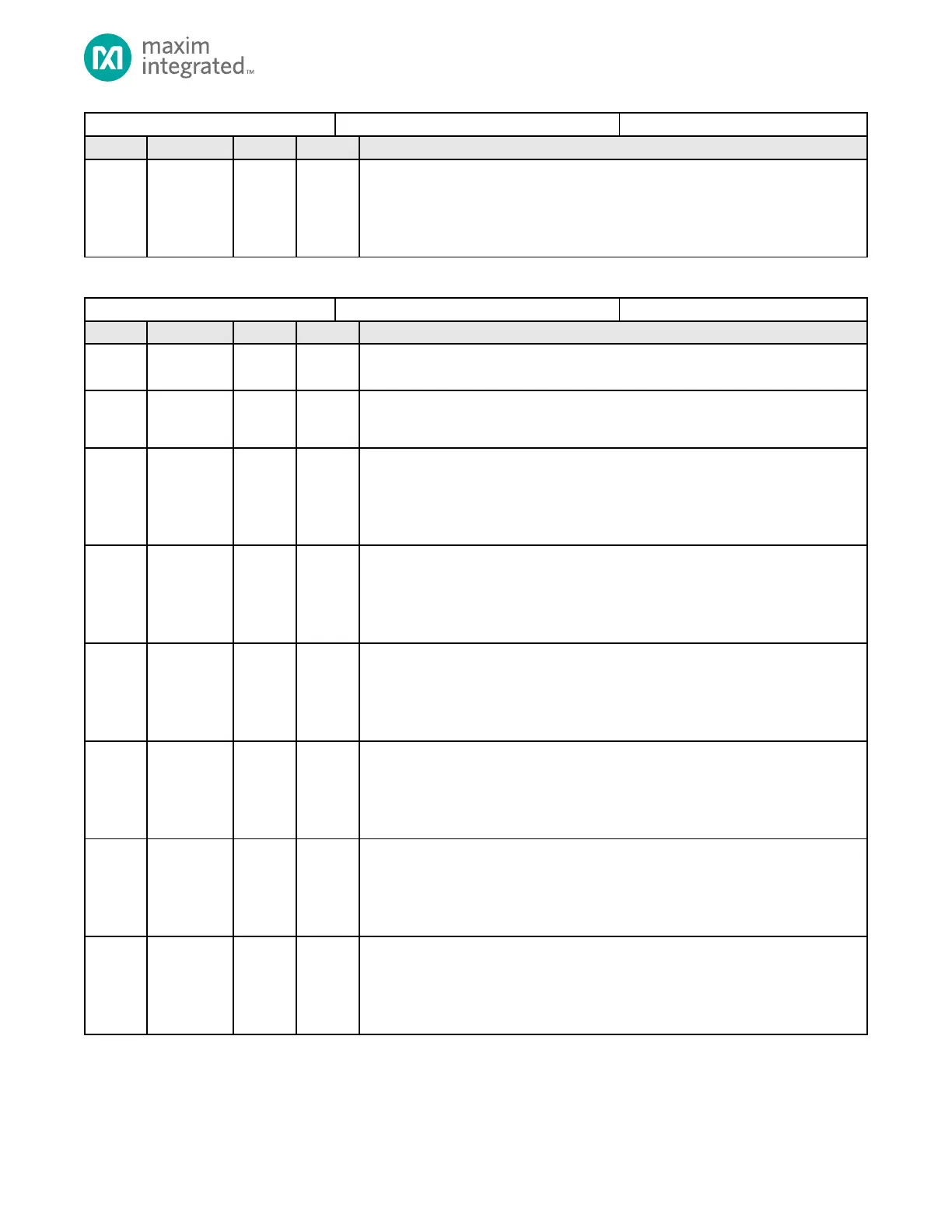

Table 17-5: Pulse Train Engine Interrupt Enable Register

PT Interrupt Enable Register

Reserved for Future Use

Do not modify this field from its default value.

PT15 Interrupt Enable

0: Disabled.

1: Enabled.

PT14 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

PT13 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

PT12 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

PT11 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

PT10 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

PT9 Interrupt Enable

Write 1 to enable the interrupt for the corresponding PT when the flag is set in the

PTG_INTFL register.

0: Disabled.

1: Enabled.

Loading...

Loading...