MAX32665-MAX32668 User Guide

Maxim Integrated Page 218 of 457

ADMA Error Status Register

ADMA Length Mismatch Error

This error occurs in the following two cases:

1) When setting Block Count Enable, the total data length specified by

the Descriptor Table is different from that specified by the Block

Count and Block Length fields.

2) Total data length is not divisible by the Block Length field.

1: Error

0: No Error

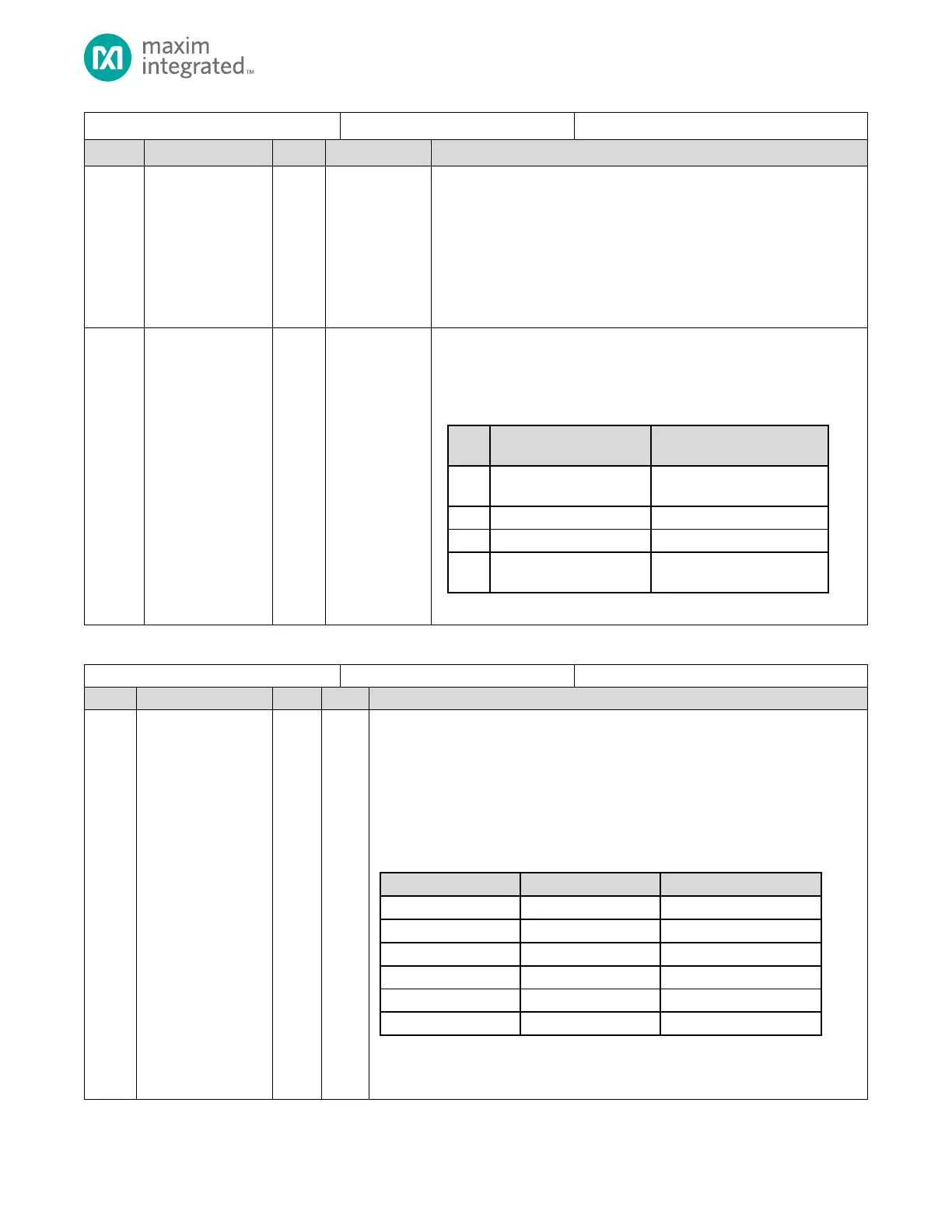

ADMA Error State

The state of the ADMA when the error condition occurred. Only valid

during data transfer for ADMA.

The following table shows the possible state values, the associated ADMA

Error State, and the contents of the SDHC_SDMA register.

ADMA Error State when

the error occurred

SYS_SDR register contents

Points next to the error

descriptor

ST_FDS (Fetch Descriptor)

Points to the error descriptor

Points next to the error

descriptor

Note: 0b10 is not a valid error state and is never set.

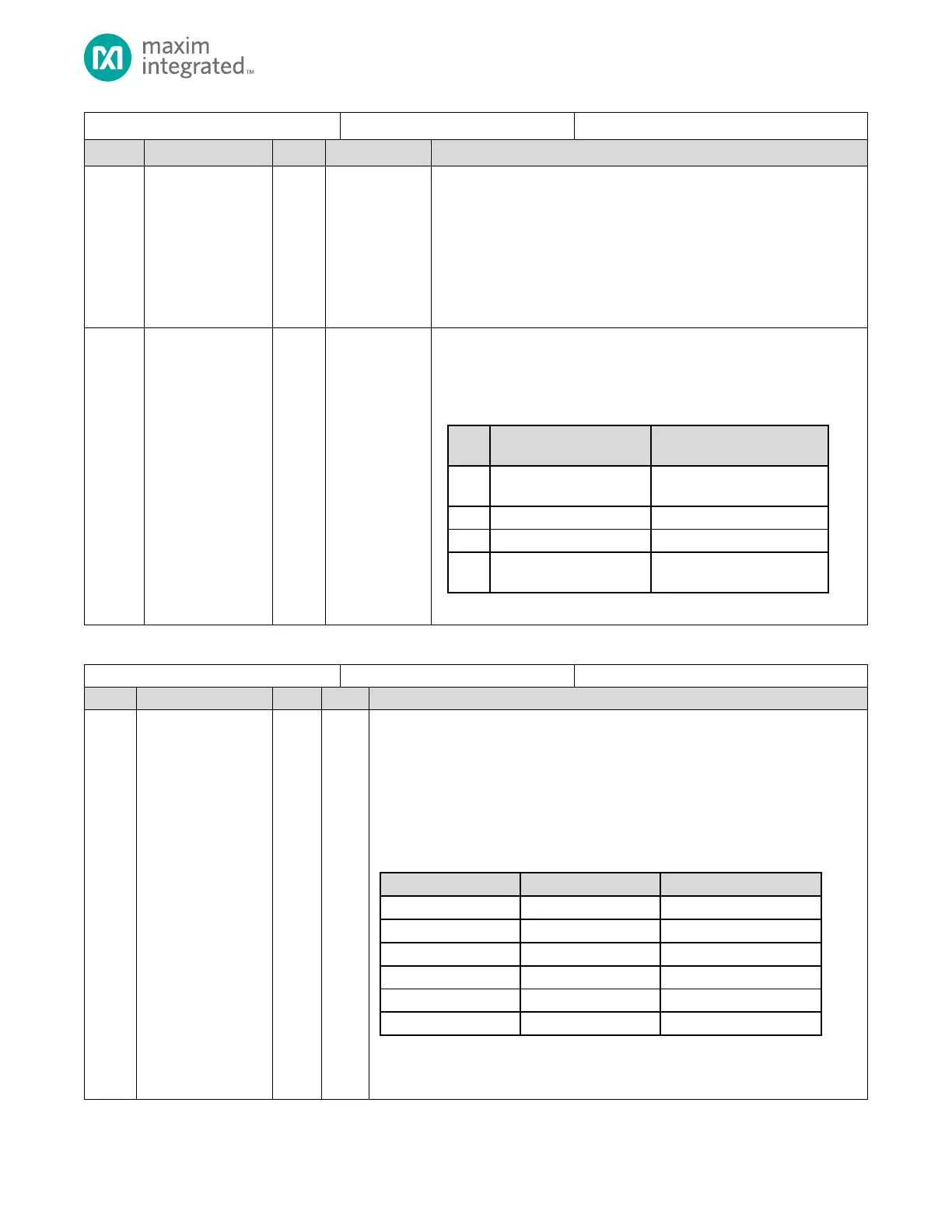

Table 8-89: SDHC ADMA System Address Register 0

ADMA System Address Register 0

ADMA System Address 0

Holds the byte address of the executing command for the Descriptor Table. The Host

Driver must set this address, made up of

<SDHC_ADMA_ADDR_1>:<SDHC_ADMA_ADDR_0>, to the start address of the

Descriptor Table. The ADMA increments this register address when fetching a

descriptor line to point to the next address. When an ADMA Error Interrupt occurs,

this register holds a valid descriptor address depending on the ADMA state. The

following table shows the 64-bit System Address for ADMA using

<SDHC_ADMA_ADDR_1>:<SDHC_ADMA_ADDR_0>.

Note: The Host Driver must program the Descriptor Table on 32-bit boundaries and set

the 32-bit boundary address to this register. ADMA2 ignores the lower two bits of this

register, assuming it to be 00b.

Loading...

Loading...