MAX32665-MAX32668 User Guide

Maxim Integrated Page 267 of 457

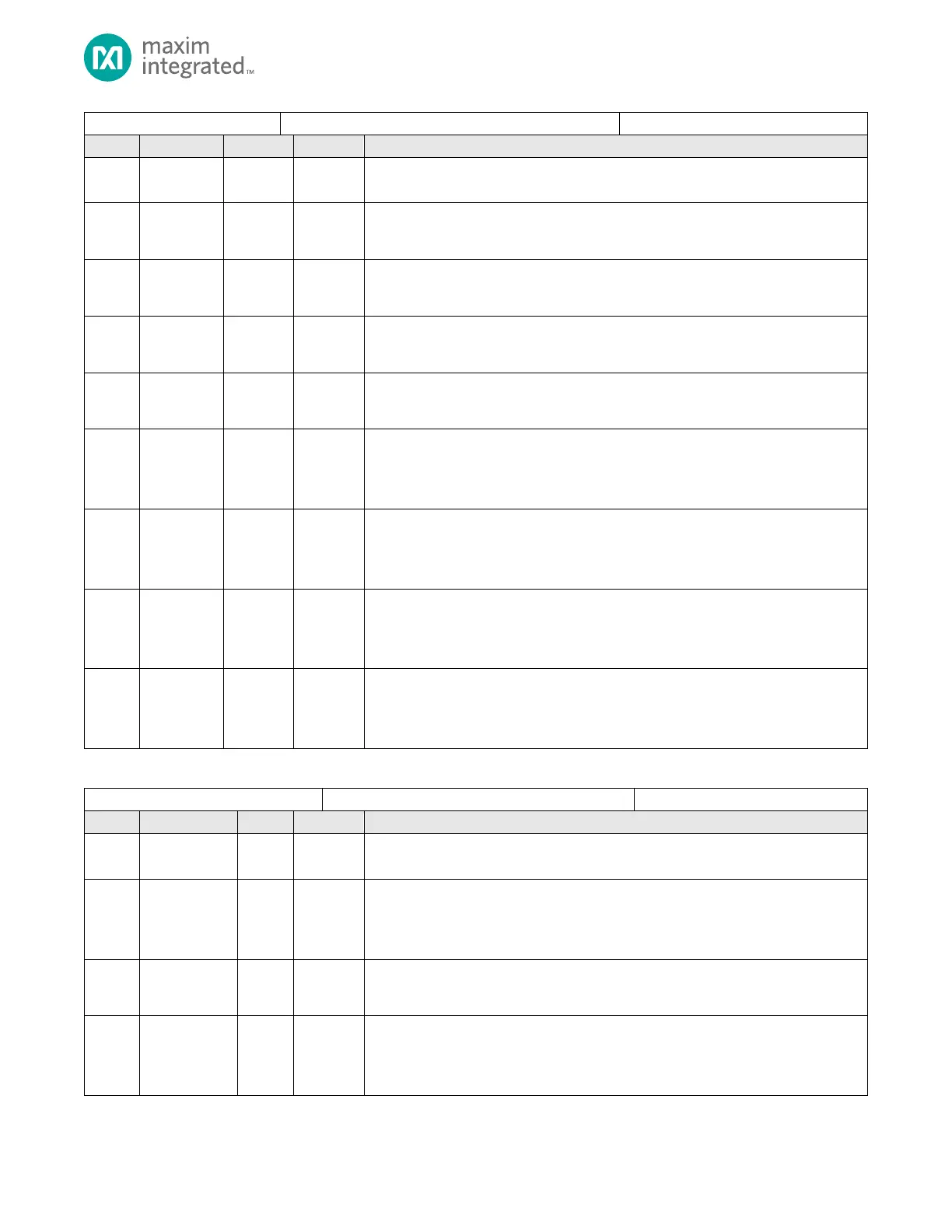

Number of characters in the Receive FIFO

Read this field to determine the number of characters in the receive FIFO.

Transmit FIFO Full Status

0: FIFO is not full.

1: FIFO is full.

Transmit FIFO Empty Status

0: FIFO is not empty.

1: FIFO is empty.

Receive FIFO Full Status

0: FIFO is not full.

1: FIFO is full.

Receive FIFO Empty Status

0: FIFO is not empty.

1: FIFO is empty.

Break Status

Set while a break condition exists.

0: A break has not been received.

1: A break condition exists.

Parity Bit State

This field returns the state of the parity bit.

0: Parity bit is 0.

1: Parity bit is 1.

Receive Busy

This field reads 1 when the UART is receiving data.

0: UART is not actively receiving data.

1: UART is actively receiving data.

Transmit Busy

This field reads 1 when the UART is transmitting data.

0: UART is not actively transmitting data.

1: UART is transmitting data.

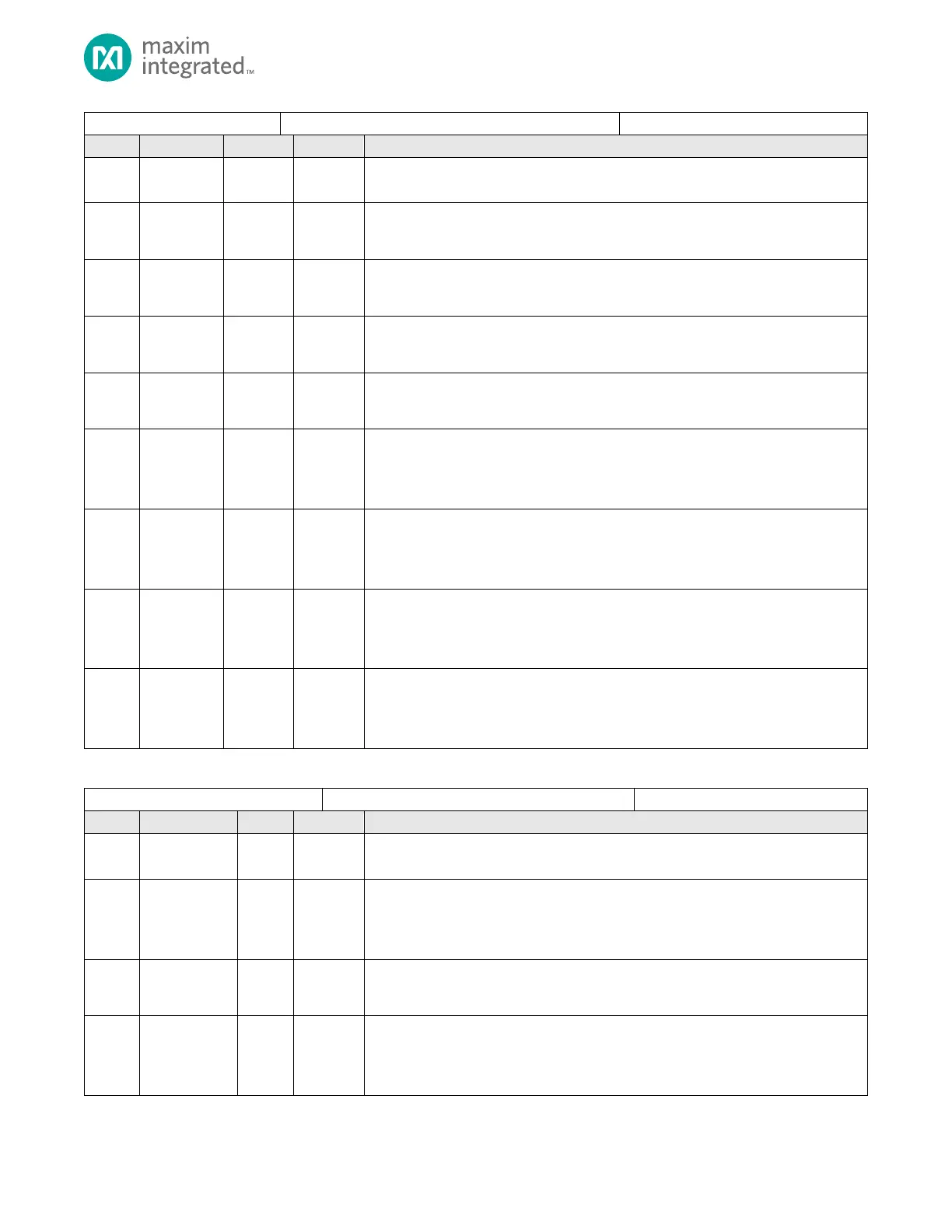

Table 12-7: UART Interrupt Enable Register

Reserved for Future Use

Do not modify this field.

BREAK End Interrupt Enable

Enables the BREAK End Detection interrupt.

0: Disabled.

1: Enabled.

Receive Timeout Interrupt Enable

0: Disabled.

1: Enabled.

Received BREAK Interrupt Enable

Enables the BREAK Detection interrupt.

0: Disabled.

1: Enabled.

Loading...

Loading...