MAX32665-MAX32668 User Guide

Maxim Integrated Page 220 of 457

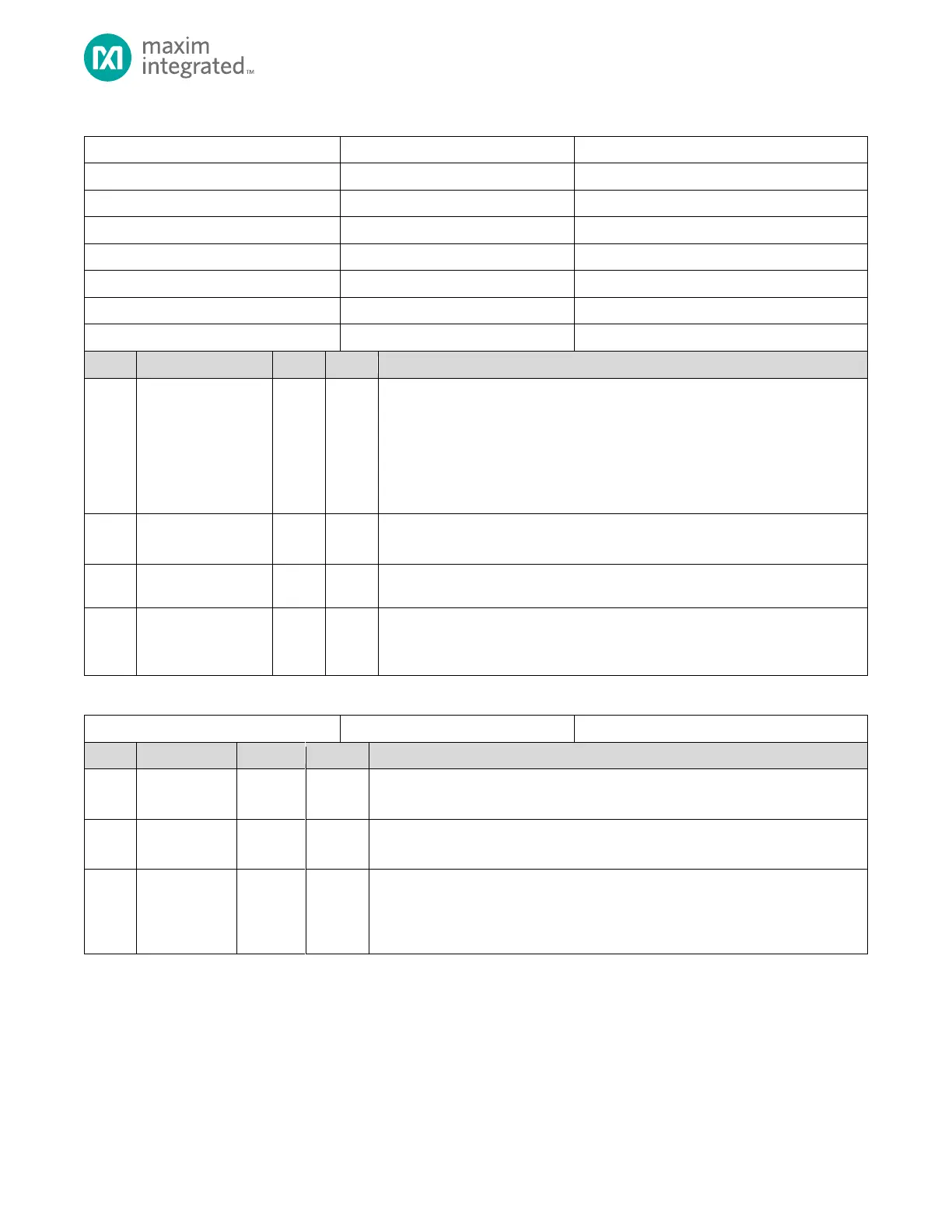

Table 8-93: SDHC Preset Value 0 to Preset Value 7 Registers

Preset Value 0 for Initialization

Preset Value 1 for Initialization

Preset Value 2 for Initialization

Preset Value 3 for Initialization

Preset Value 4 for Initialization

Preset Value 5 for Initialization

Preset Value 6 for Initialization

Preset Value 7 for Initialization

Driver Strength Select Value

Driver strength is supported by 1.8V signaling bus speed modes. This field is not

used for 3.3V signaling.

0b00: Driver Type B is selected

0b01: Driver Type A is selected

0b10: Driver Type C is selected

0b11: Driver Type D is selected

Reserved for Future Use

Do not modify this field.

Clock Generator Select Value

0: Programmable clock generator is not supported

SDCLK Frequency Select Value

10-bit preset value to set the SDCLK Frequency Select field in the Clock Control

register (SDHC_CLK_CN.upper_sdclk_freq_sel and SDHC_CLK_CN.sdclk_freq_sel)

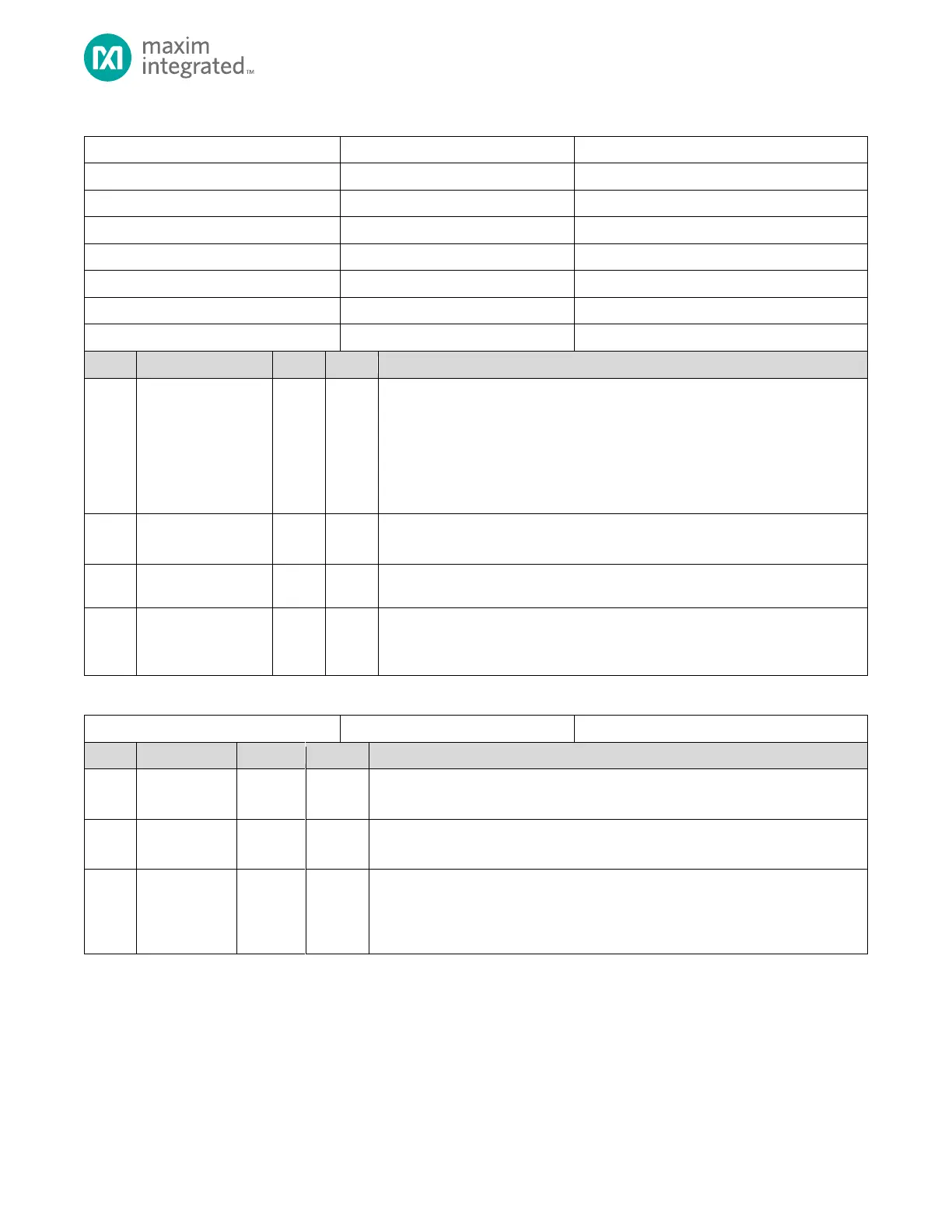

Table 8-94: SDHC Slot Interrupt Status Register

Slot Interrupt Status Register

Reserved for Future Use

Do not modify this field.

Reserved for Future Use

Do not modify this field.

Interrupt Signals

Indicates the logical OR of Interrupt Signal and Wakeup Signal for the single slot. Only

one slot is defined for the MAX32665—MAX32668, slot 0. Reset by POR and by

software reset for all (SDHC_SW_RESET.reset_all).

Loading...

Loading...