MAX32665-MAX32668 User Guide

Maxim Integrated Page 315 of 457

14.6 Register Details

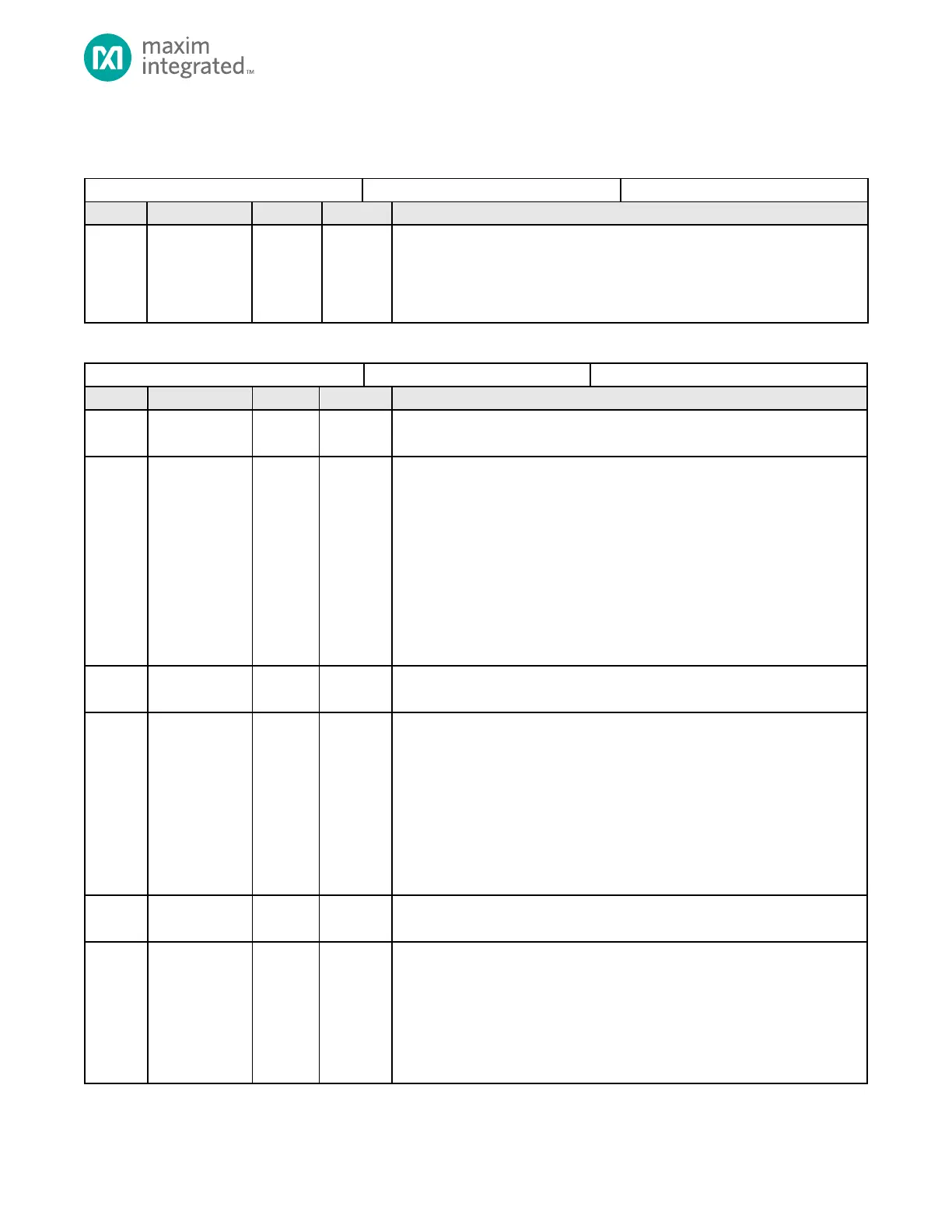

Table 14-7: QSPIn FIFO Data Register

QSPIn FIFO Data Register

This register is used for the QSPI Transmit and Receive FIFO. Reading from this

register returns characters from the Receive FIFO and writing to this register adds

characters to the Transmit FIFO. Read and write this register in either 1-byte, 2-

byte or 4-byte widths only.

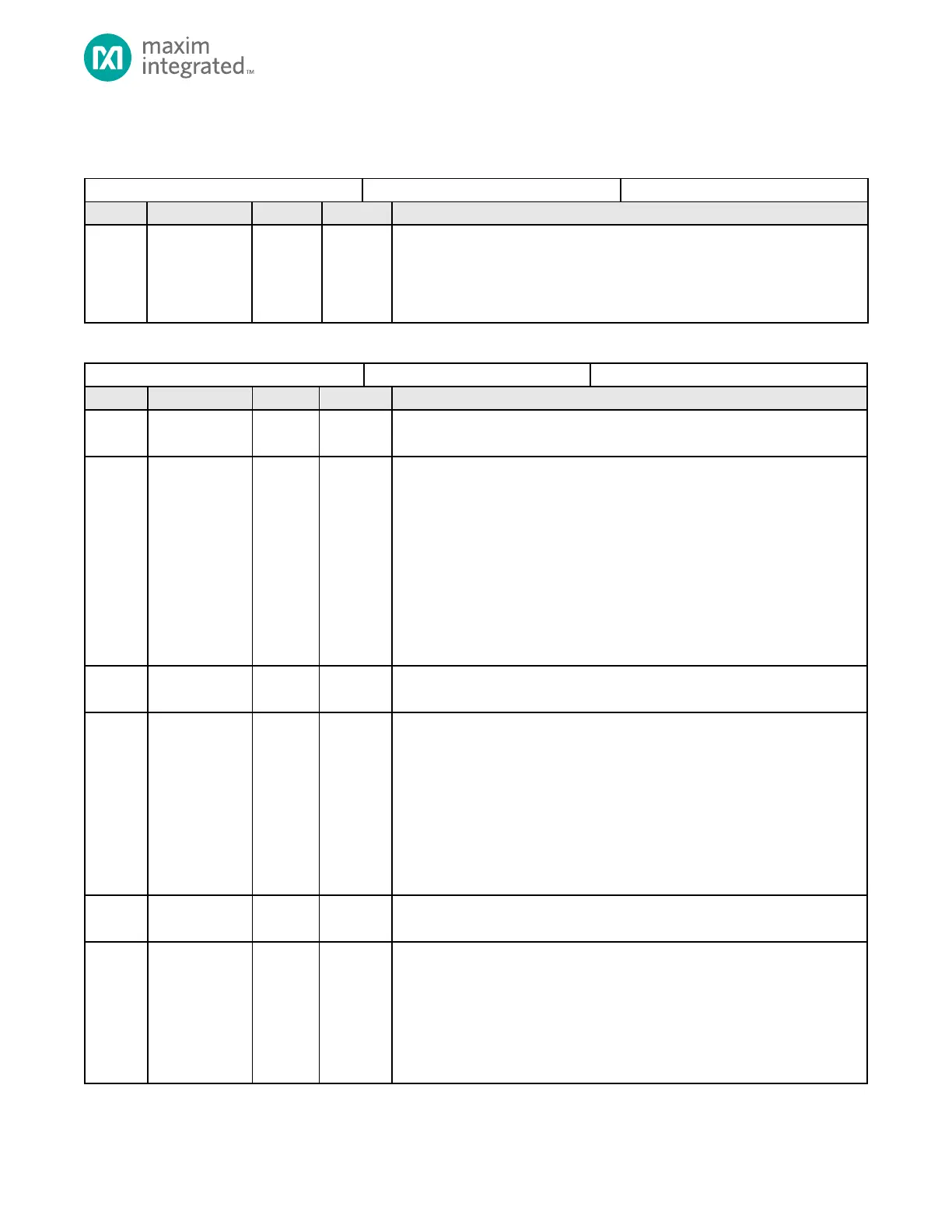

Table 14-8: QSPIn Control 0 Register

Reserved for Future Use

Do not modify this field.

Master Slave Select

The QSPIn includes up to three slave select lines for each port. This field selects

which slave select pin is active when the next SPI transaction is started

(QSPIn_CTRL0.start = 1). One or more slave select pins can be selected for each

SPI transaction by setting the bit for each slave select pin. For example, use

QSPIn_SS0 and QSPIn_SS2 by setting this field to 0b101.

0b001: QSPIn_SS0

0b010: QSPIn_SS1

0b100: QSPIn_SS2

Note: This field is only used when the QSPIn is configured for Master Mode

(QSPIn_CTRL0.master = 1).

Reserved for Future Use

Do not modify this field.

Master Slave Select Control

This field controls the behavior of the slave select pins at the completion of a

transaction. The default behavior, ss_ctrl = 0, deasserts the slave select pin at the

completion of the transaction. Set this field to 1 to leave the slave select pins

asserted at the completion of the transaction. If the external device supports this

behavior, leaving the slave select pins asserted allows multiple transactions

without the delay associated with deassertion of the slave select pin between

transactions.

0: Slave Select is deasserted at the end of a transmission

1: Slave Select stays asserted at the end of a transmission

Reserved for Future Use

Do not modify this field.

Master Start Data Transmission

Set this field to 1 to start a SPI master mode transaction.

0: No master mode transaction active.

1: Master initiates a data transmission. Ensure that all pending transactions are

complete before setting this field to 1.

Note: This field is only used when the QSPIn is configured for Master Mode

(QSPIn_CTRL0.master = 1).

Loading...

Loading...