MAX32665-MAX32668 User Guide

Maxim Integrated Page 102 of 457

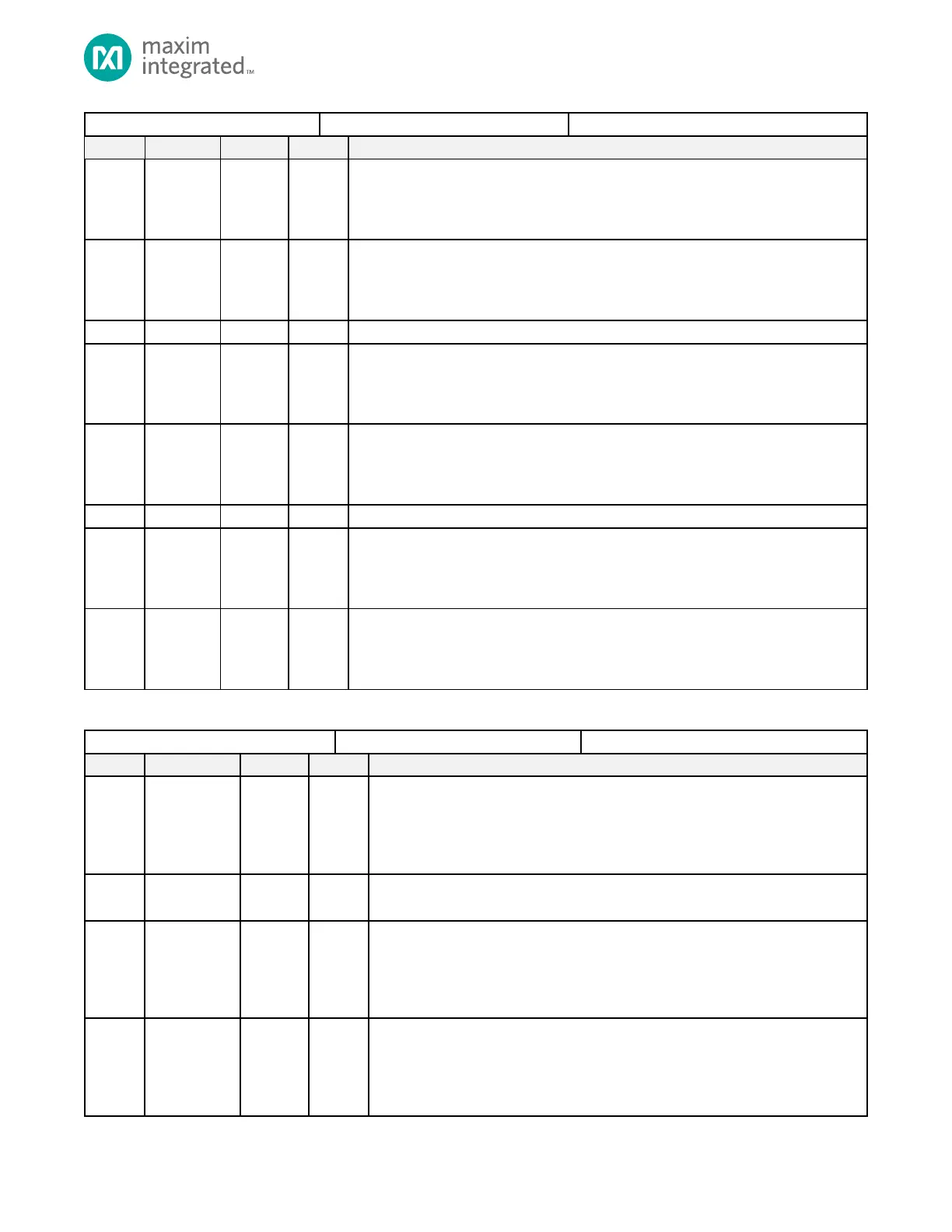

One-Wire Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

SDHC Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

XSPI Master Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

SPI-XIPF Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

Pulse Train Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

I2C1 Reset

Write 1 to initiate the operation.

0: Operation complete.

1: Operation in progress.

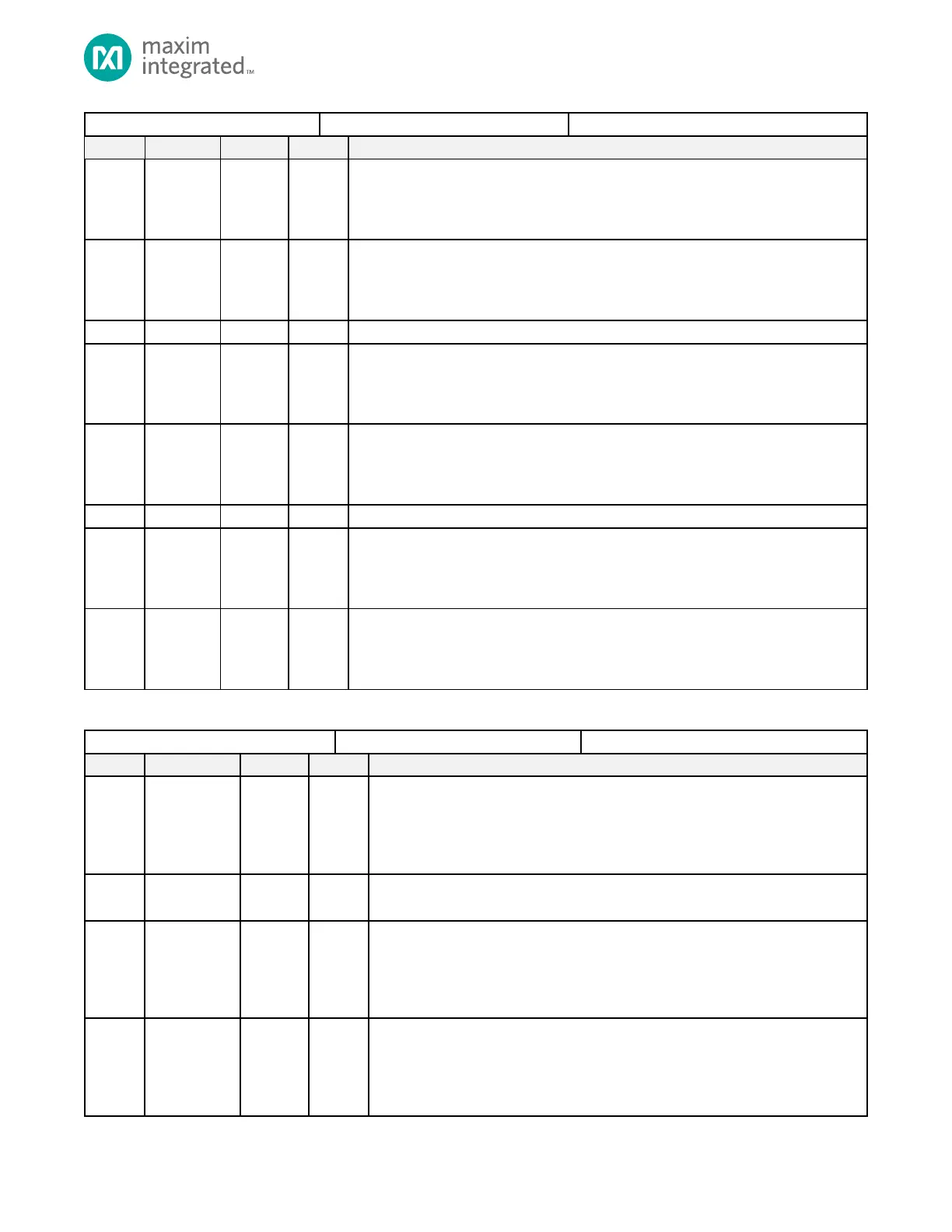

Table 4-64: Peripheral Clock Disable Register 1

Peripheral Clock Disable 1

CPU1 Clock Disable

Disabling the clock disables functionality while also saving power. Associated register

states are retained but read and write access is blocked.

0: Enabled.

1: Disabled.

Reserved

Do not modify this field.

WDT2 Clock Disable

Disabling the clock disables functionality while also saving power. Associated register

states are retained but read and write access is blocked.

0: Enabled.

1: Disabled.

Watchdog Timer 1 Disable

Disabling the clock disables functionality while also saving power. Associated register

states are retained but read and write access is blocked.

0: Enabled.

1: Disabled.

Loading...

Loading...