MAX32665-MAX32668 User Guide

Maxim Integrated Page 418 of 457

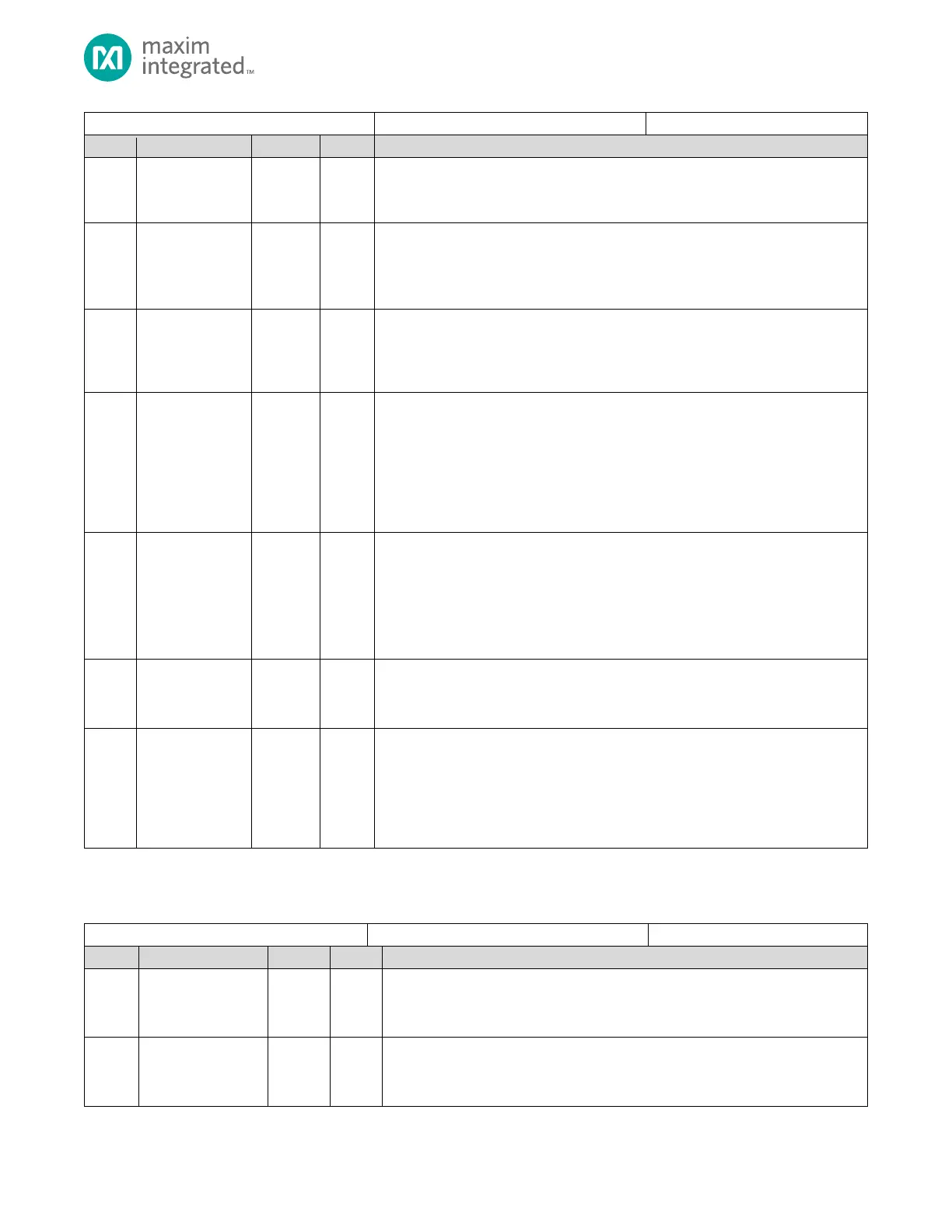

USBHS IN Endpoint Lower Control and Status

Clear IN Endpoint Data Toggle

1: Clear the IN Endpoint data toggle to 0.

Note: Automatically cleared after set.

Read STALL Handshake Sent Status

Automatically set when a STALL handshake is transmitted, at which time the IN

FIFO is flushed, and USBHS_INCSRL.inpktrdy is cleared.

Note: Write a 0 to clear.

Send STALL Handshake

1: Respond to an IN token with a STALL handshake.

0: Terminate STALL handshake

Note: Ignored for Isochronous transfers.

Flush Next Packet from IN FIFO

1: Flush the next packet to be transmitted from the IN FIFO. This also clears the bit

field USBHS_INCSRL.inpktrdy. This must only be set when

USBHS_INCSRL.inpktrdy = 1, or FIFO data corruption might occur.

Note: If the IN FIFO contains two packets, set the flushfifo field twice to clear both

packets.

Note: Automatically cleared when the packet is flushed.

Read IN FIFO Underrun Error Status

Isochronous Mode: Automatically set if the IN FIFO is empty (inpktrdy = 0), an IN

token has been received, and a zero-length data packet has been sent.

Bulk or Interrupt Modes: Automatically set when an IN token is received, and a

NAK is sent.

Note: Write a 0 to clear.

Read FIFO Not Empty Status

Automatically set when there is at least one packet in the IN FIFO.

Note: Write a 0 to clear.

IN Packet Ready

1: Write a 1 after writing a data packet to the IN FIFO.

Automatically cleared when the data packet is transmitted. If double-buffering is

enabled, this bit is automatically cleared when there is space for a second packet in

the FIFO.

Note: This bit field is also controlled by USBHS_INCSRU.autoset.

21.12.5 USBHS Endpoint 0 Control Status Register

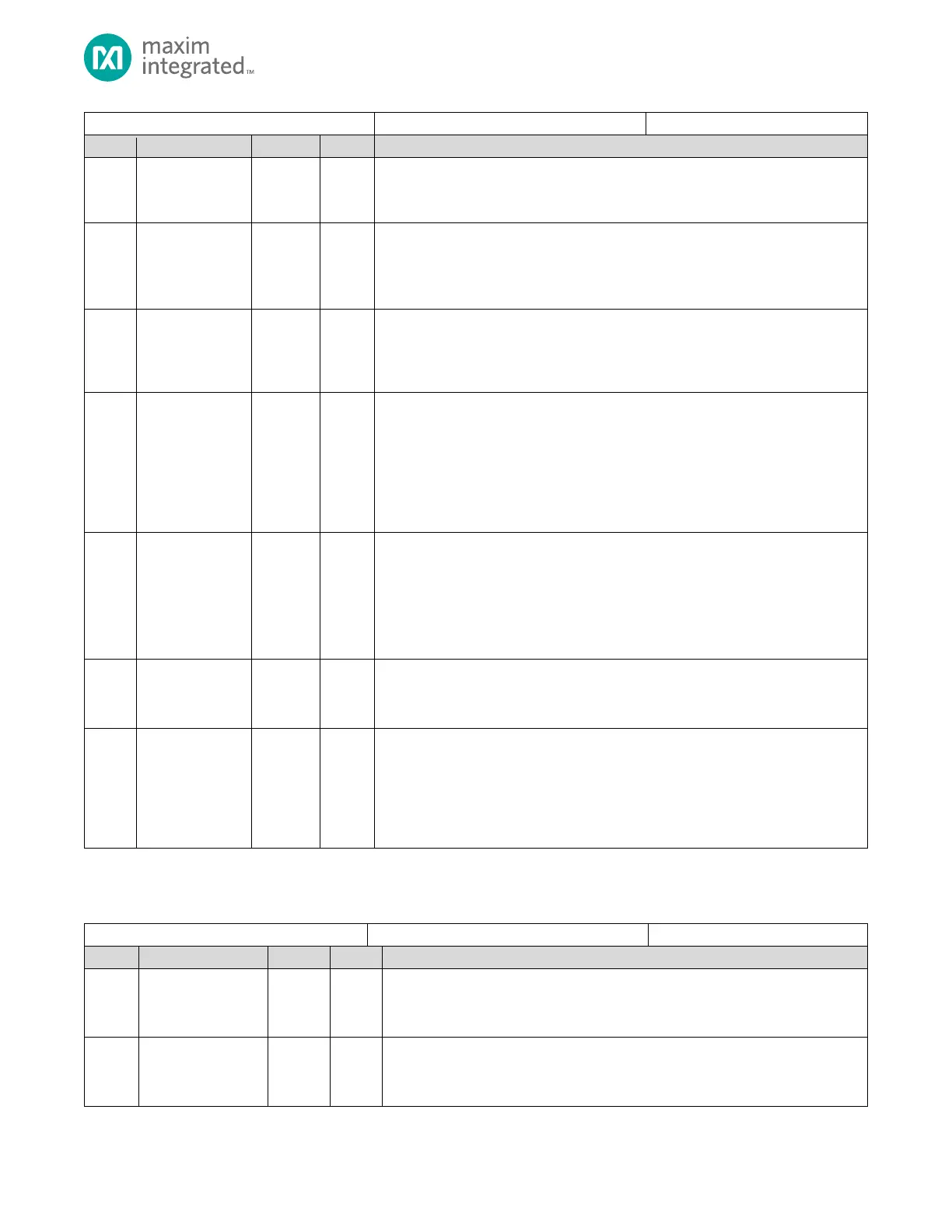

Table 21-20: USBHS Endpoint 0 Control Status Register

USBHS Endpoint 0 Control Status

Clear EP0 Setup End Bit

Write a 1 to clear the setupend bit.

Note: Automatically cleared after being set.

Clear EP0 Out Packet Ready Bit

Write a 1 to clear the outpktrdy bit (below).

Note: Automatically cleared after being set.

Loading...

Loading...