MAX32665-MAX32668 User Guide

Maxim Integrated Page 320 of 457

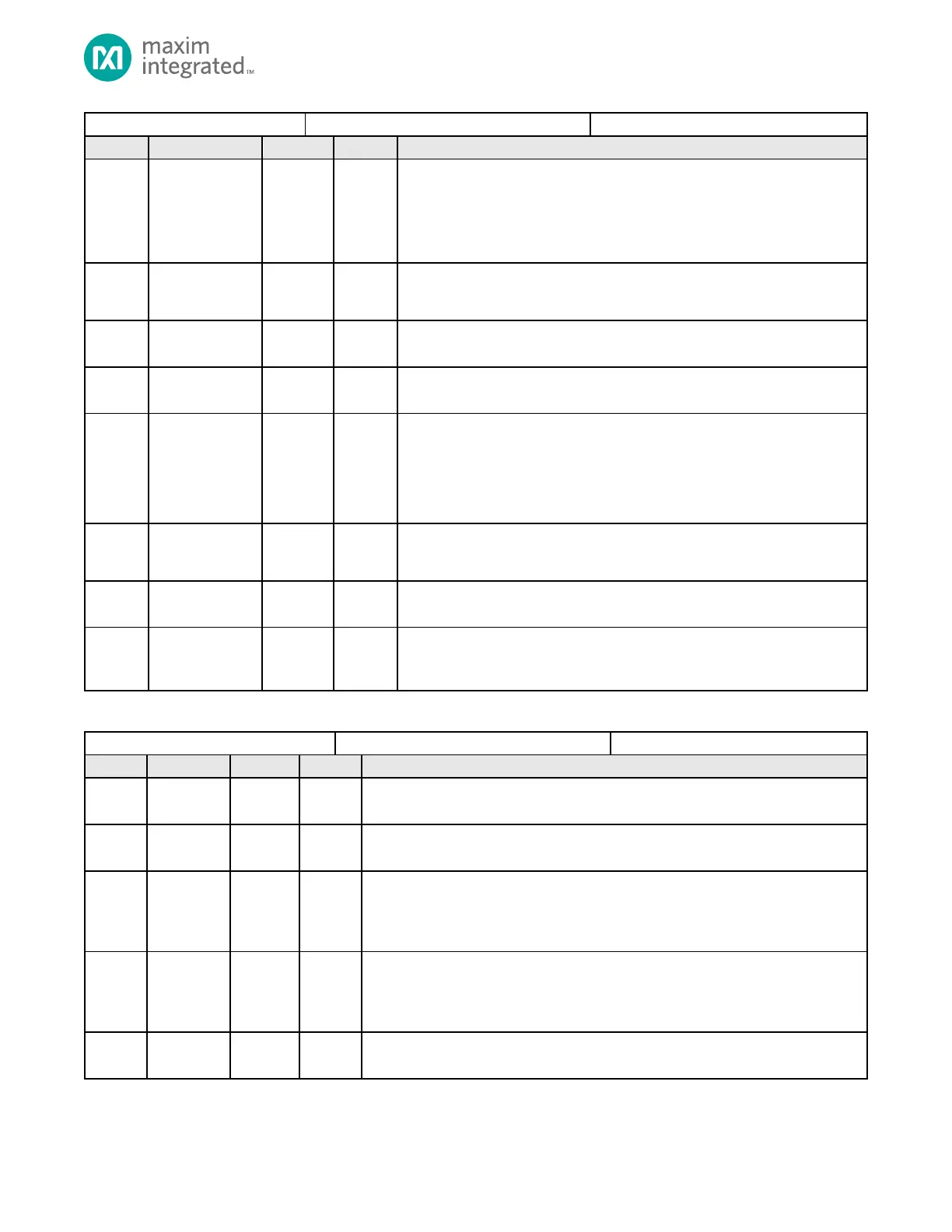

QSPIn DMA Control Register

RX FIFO Threshold Level

Set this value to the desired RX FIFO threshold level. When the RX FIFO contains

the number of bytes or greater than this field, a DMA request is triggered, and

QSPIn_INT_FL.rx_thresh is set. Valid values are 0 to 30.

Note: 31 is an invalid setting and reserved for future use.

TX DMA Enable

0: Disabled. Any pending DMA requests are cleared

1: TX DMA is enabled

Reserved for Future Use

Do not modify this field.

Number of Bytes in the TX FIFO

Read this field to determine the number of bytes currently in the TX FIFO.

TX FIFO Clear

Set this bit to clear the TX FIFO and all TX FIFO flags in the QSPIn_INT_FL register.

Note: The TX FIFO should be disabled (QSPIn_DMA.tx_fifo_en = 0) prior to setting

this field.

Note: Setting this field to 0 has no effect.

TX FIFO Enabled

0: Disabled

1: Enabled

Reserved for Future Use

Do not modify this field.

TX FIFO Threshold Level

When the TX FIFO count (QSPIn_DMA.tx_fifo_cnt) falls below this value, a DMA

request is triggered and QSPIn_INT_FL.tx_thresh is set.

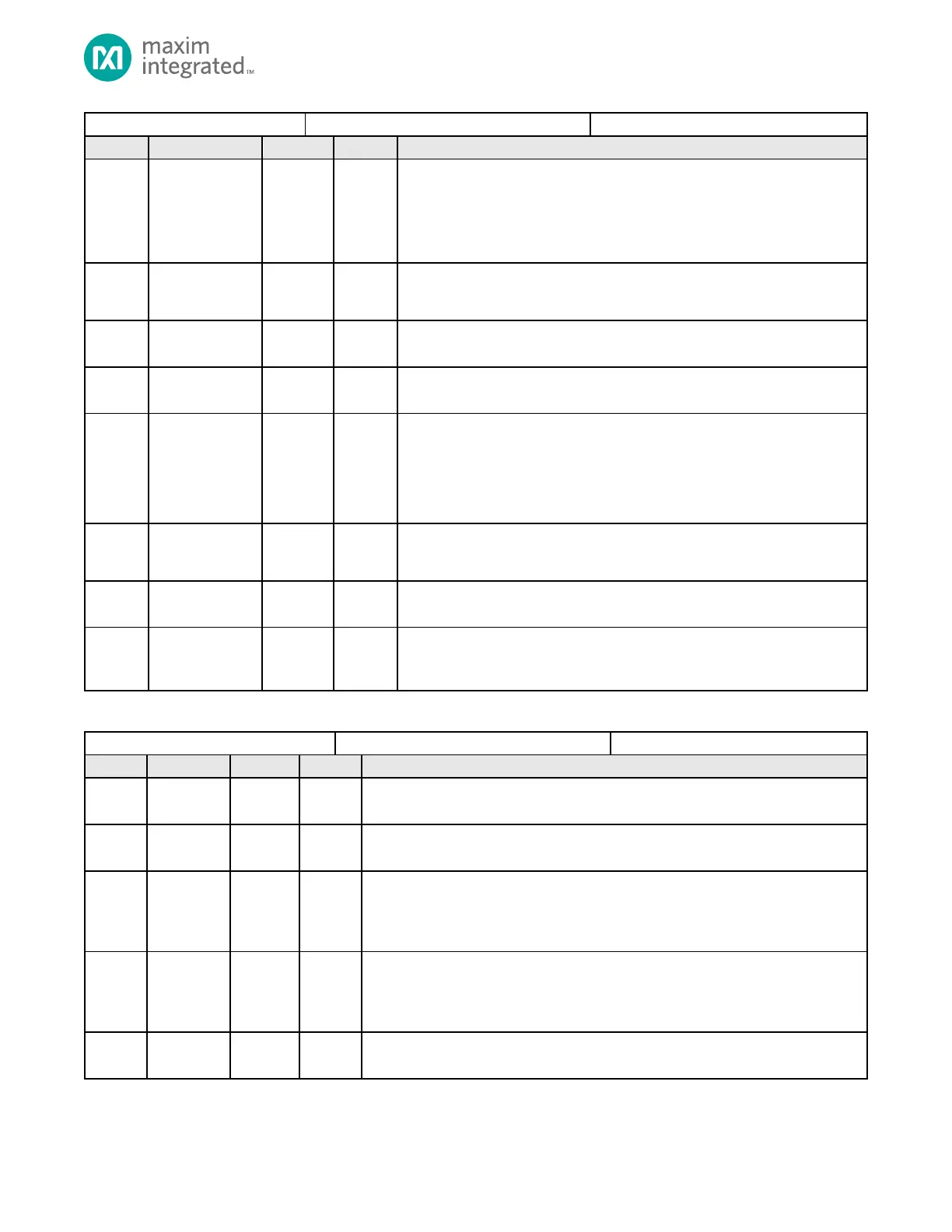

Table 14-14: QSPIn Interrupt Status Flags Registers

QSPIn Interrupt Status Flags Register

Reserved for Future Use

Do not modify this field.

RX FIFO Underrun Flag

Set when a read is attempted from an empty RX FIFO.

RX FIFO Overrun Flag

Set if SPI is in Slave Mode, and a write to a full RX FIFO is attempted. If the SPI is in

Master Mode, this bit is not set as the SPI stalls the clock until data is read from the RX

FIFO.

TX FIFO Underrun Flag

Set if SPI is in Slave Mode, and a read from empty TX FIFO is attempted. If SPI is in

Master Mode, this bit is not set as the SPI stalls the clock until data is written to the

empty TX FIFO.

TX FIFO Overrun Flag

Set when a write is attempted to a full TX FIFO.

Loading...

Loading...