MAX32665-MAX32668 User Guide

Maxim Integrated Page 68 of 457

4.8.2.1 RAM LIGHTSLEEP

RAM can be placed in a low power mode, referred to as LIGHTSLEEP, using the Memory Clock Control Register,

GCR_MEM_CLK. LIGHTSLEEP gates off the clock to the RAM and makes the RAM unavailable for read/write operations,

while memory contents are retained, reducing power consumption. LIGHTSLEEP is available for the 6 Data RAM blocks and

the ECC RAM block, the USB FIFO, Crypto RAM, ICC0 RAM, ICC1 RAM, SFCC RAM and the SRCC RAM. RAM contents are

available when exiting LIGHTSLEEP mode.

4.8.2.2 RAM Shut Down

RAM memories can individually be shut down further reducing the power consumption for the device. Shutting down a

memory gates off the clock and removes power to the memory. Shutting down a memory invalidates (destroys) the

contents of the memory and results in a POR of the memory when it is enabled. RAM memory shut down is configured

using the PWRSEQ_LPMEMSD register.

4.9 Miscellaneous Control Registers

This set of control registers provides control for system related aspects such as ECC enable, Comparator enable, Square

Wave Out enable, Power Down signaling enable, Power Control, Rest Pullup control, and SIMO Clock enable.

See Table 3-1: APB Peripheral Base Address Map for the Miscellaneous Control Peripheral Base Address.

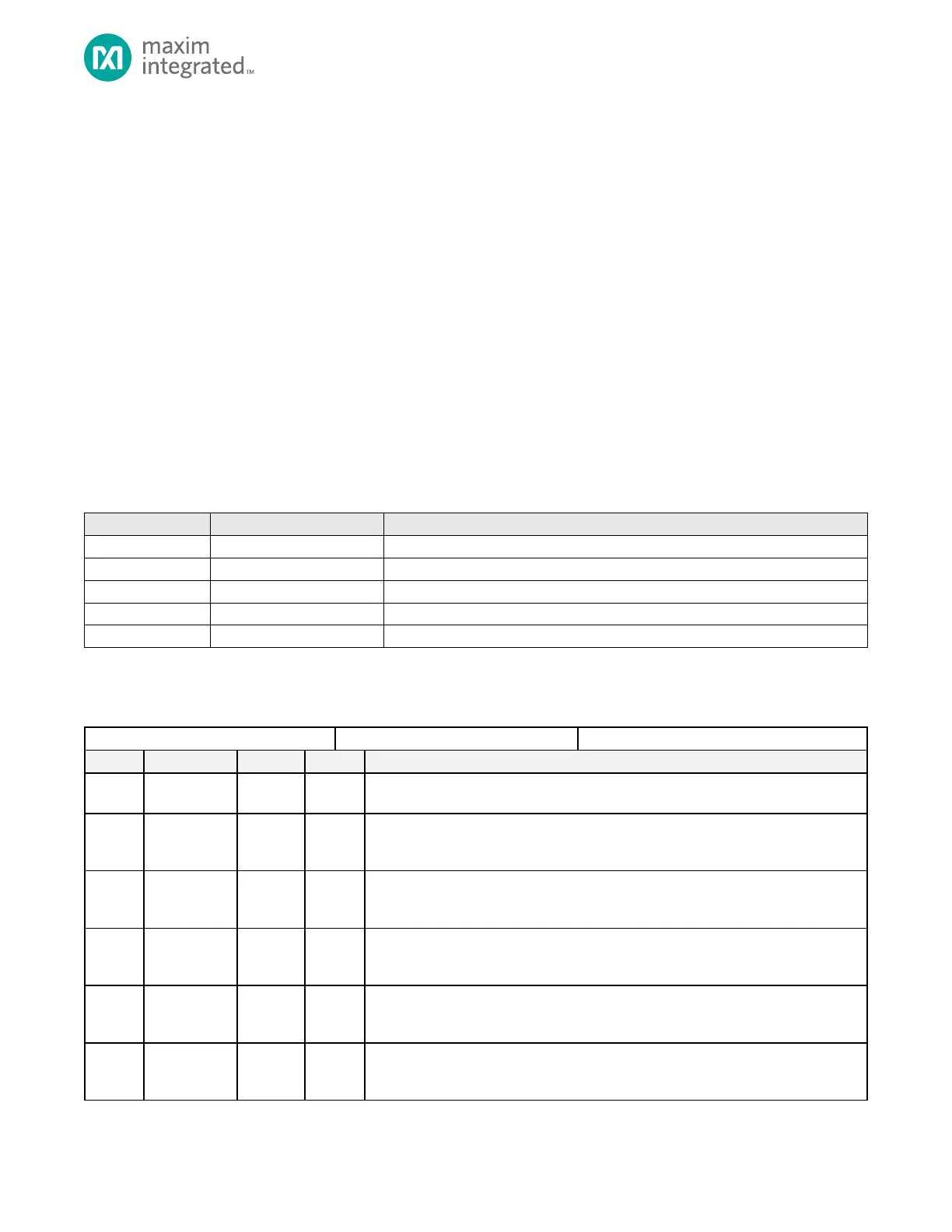

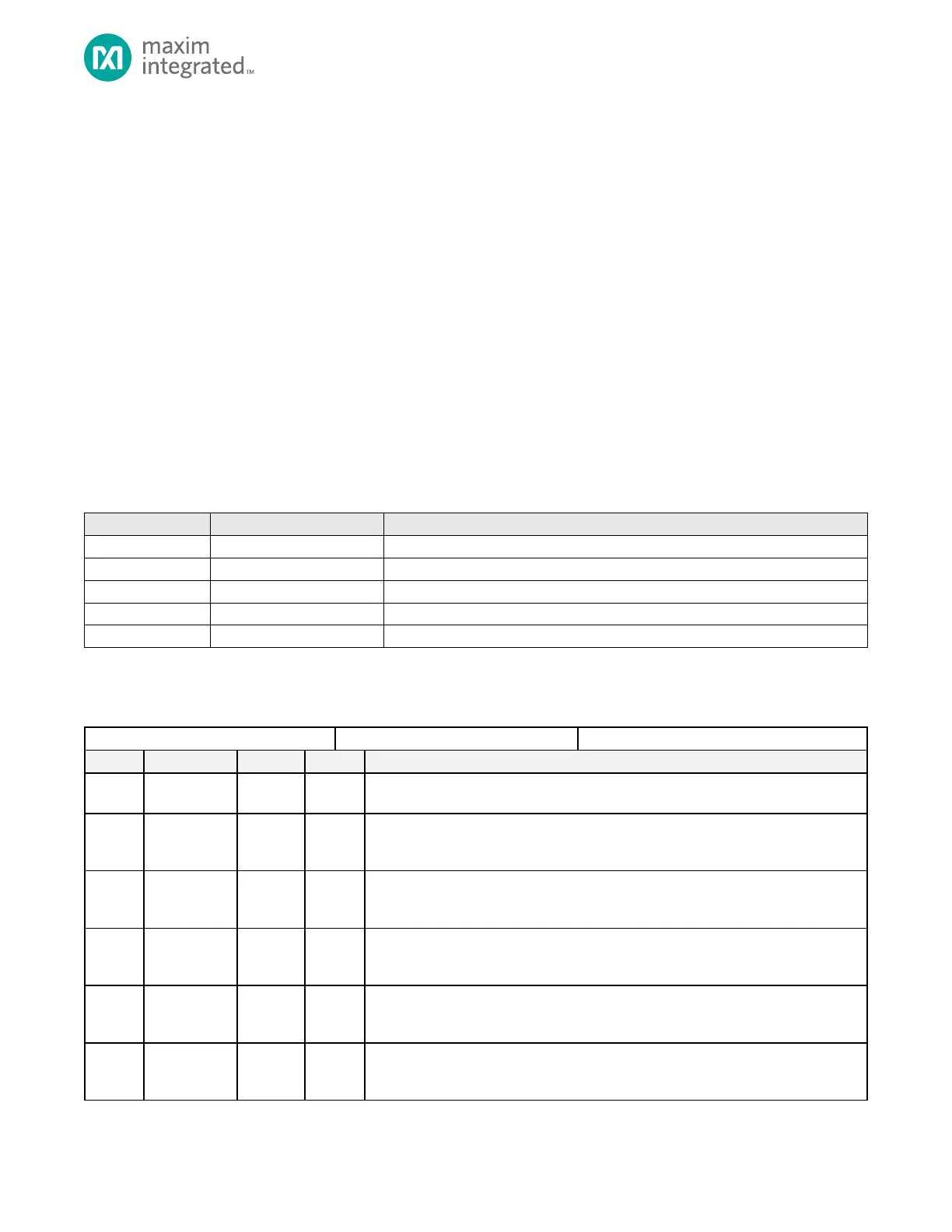

Table 4-14 Miscellaneous Control Register Summary

Loading...

Loading...