MAX32665-MAX32668 User Guide

Maxim Integrated Page 424 of 457

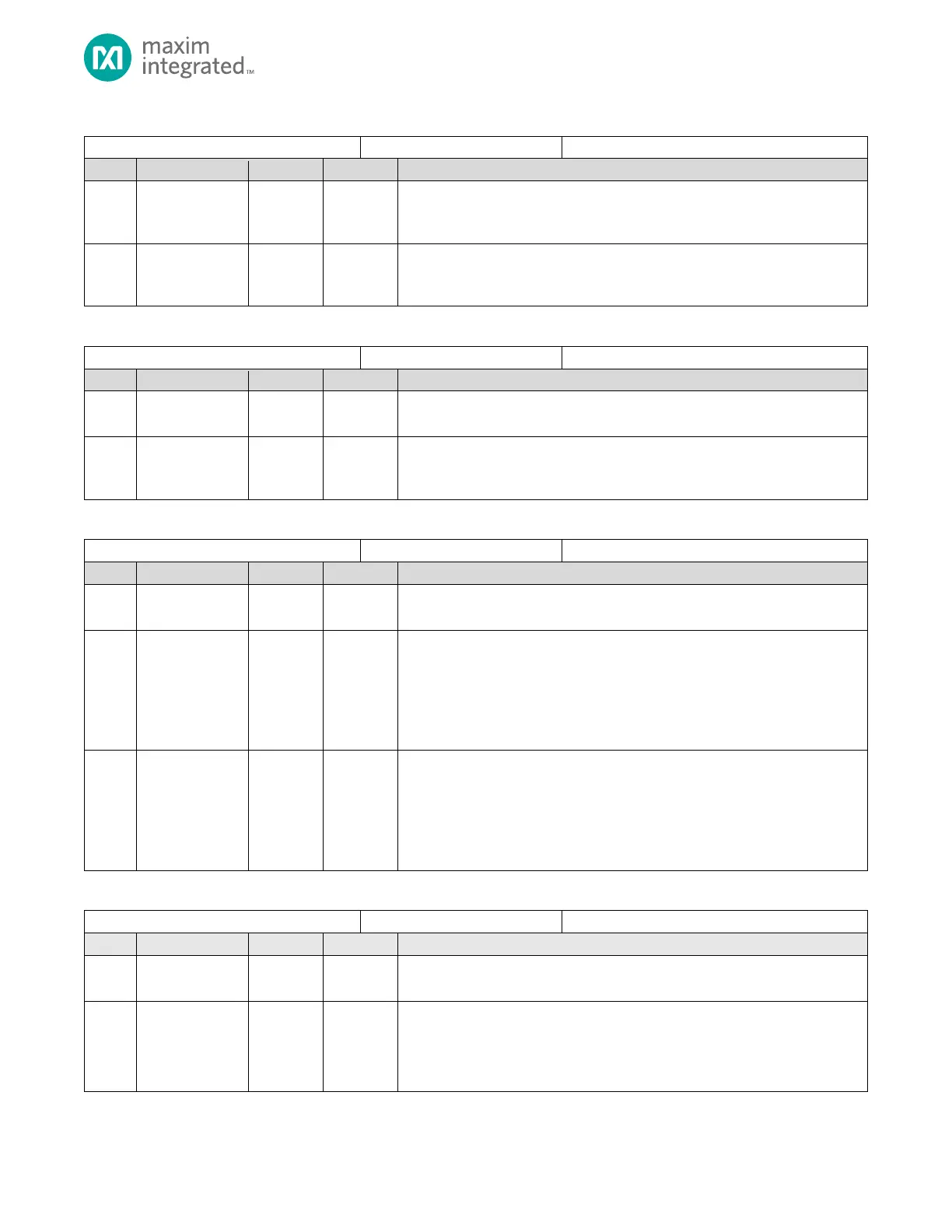

Table 21-28: USBHS Endpoint Count Info Register

USBHS Endpoint Count Info

Number of OUT Endpoints

There are 11 OUT endpoints in this USBHS peripheral.

0xB: 11 OUT Endpoints.

Number of IN Endpoints

Returns the number of IN endpoints in this USBHS peripheral.

0xB: 11 IN Endpoints

Table 21-29: USBHS RAM Info Register

Reserved for Future Use

Do not modify this field.

Number of RAM Address Bits

The width of the RAM address bus in this USBHS module. The width is 12 bits.

0xC: 12-bit-wide RAM address supported in the USB HS peripheral.

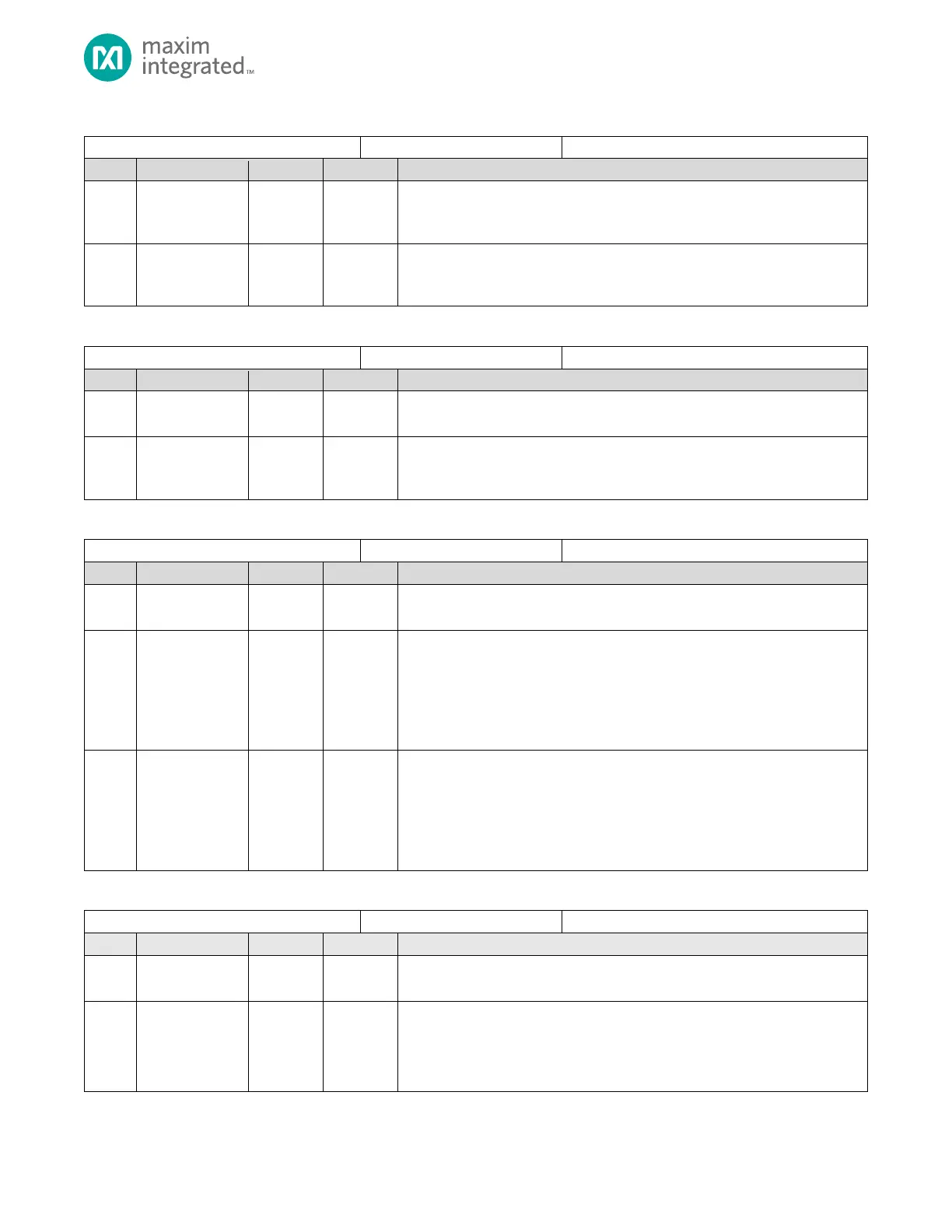

Table 21-30: USBHS Soft Reset Control Register

Reserved for Future Use

Do not modify this field.

Reset the USB PHY.

Write a 1 to reset the USB PHY.

This field is cleared by hardware automatically after a 1 is written and the USB

PHY is reset.

0: USB PHY reset complete or not initiated.

1: Write 1 to reset the USB PHY.

Reset the USB Controller.

Write 1 to reset the USBHS controller.

This field is cleared by hardware automatically after a 1 is written and the USBHS

controller is reset.

0: USBHS controller reset complete or not initiated.

1: Write 1 to reset the USBHS controller.

Table 21-31: USBHS Early DMA Register

Reserved for Future Use

Do not modify this field.

Early DMA IN Endpoints Enable

0: DMA Request signal for all IN endpoints is deasserted when USBHS_INMAXP

bytes have been written to an endpoint.

1: DMA Request signal for all IN endpoints is deasserted when

bytes have been written to an endpoint.

Loading...

Loading...