MAX32665-MAX32668 User Guide

Maxim Integrated Page 366 of 457

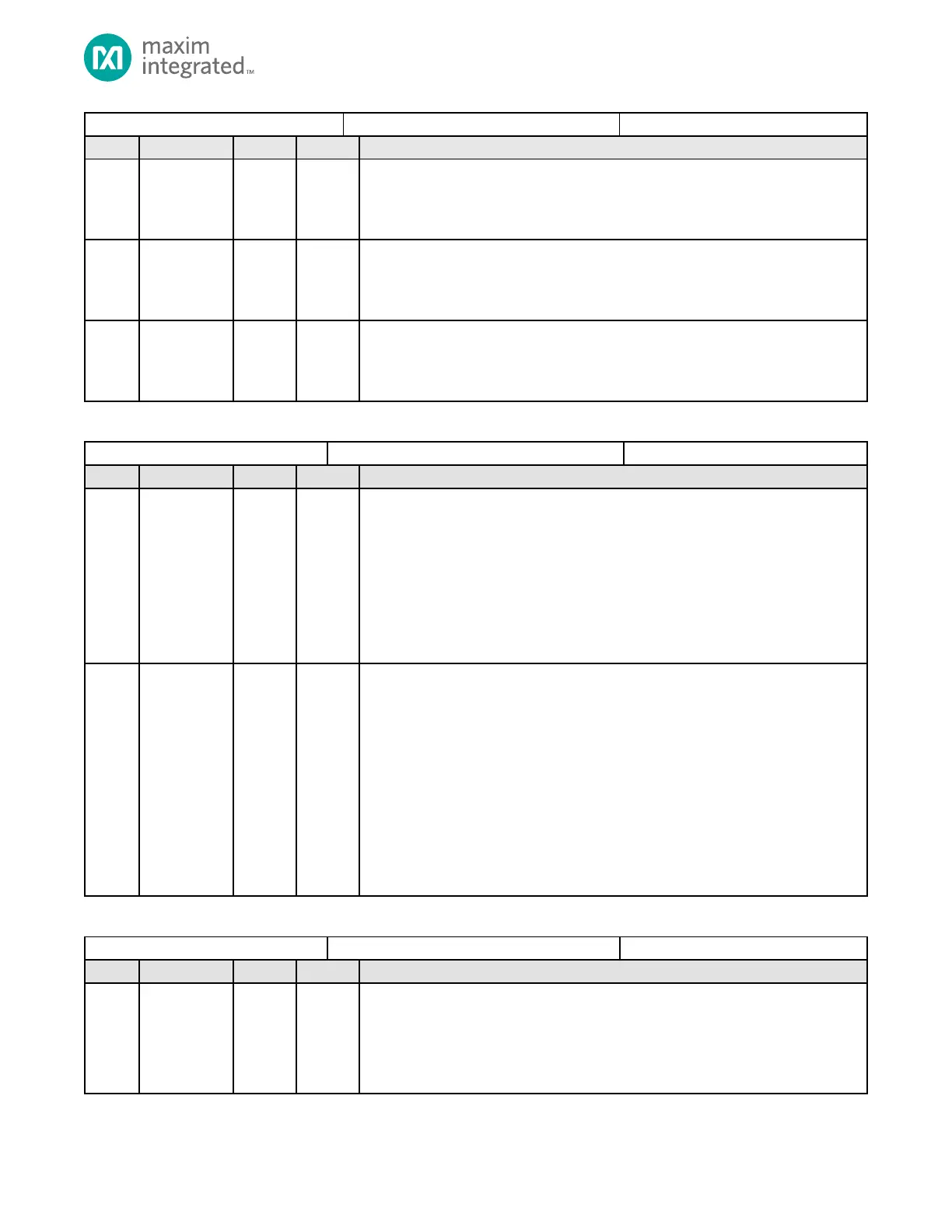

Pulse Train Engine Safe Disable Register

Safe Disable Control for PT2

Writing a 1 clears PTG_ENABLE.enable_pt2.

1: Disable corresponding pulse train

0: No effect

Safe Disable Control for PT1

Writing a 1 clears PTG_ENABLE.enable_pt1.

1: Disable corresponding pulse train

0: No effect

Safe Disable Control for PT0

Writing a 1 clears PTG_ENABLE.enable_pt0.

1: Disable corresponding pulse train

0: No effect

Table 17-8: Pulse Train Engine Configuration Register

Pulse Train Configuration Register

Square Wave or Pulse Train Output Mode

Sets either pulse train mode with length, or Square Wave mode.

0: Pulse train mode, 32-bits long

1: Square Wave mode

2: Pulse train mode, 2-bits long

3: Pulse train mode, 3-bits long

… etc …

31: Pulse train mode, 31-bits long

Note: If this field is set to 1, Square Wave mode, the PTn_LENGTH register is not used.

Pulse Train Enable and Rate Control

Defines the rate at which the output for PTn changes state by setting the

divisor of the PT Clock, where:

0: Output halted

1:

2:

3:

…

0x7FFFF:

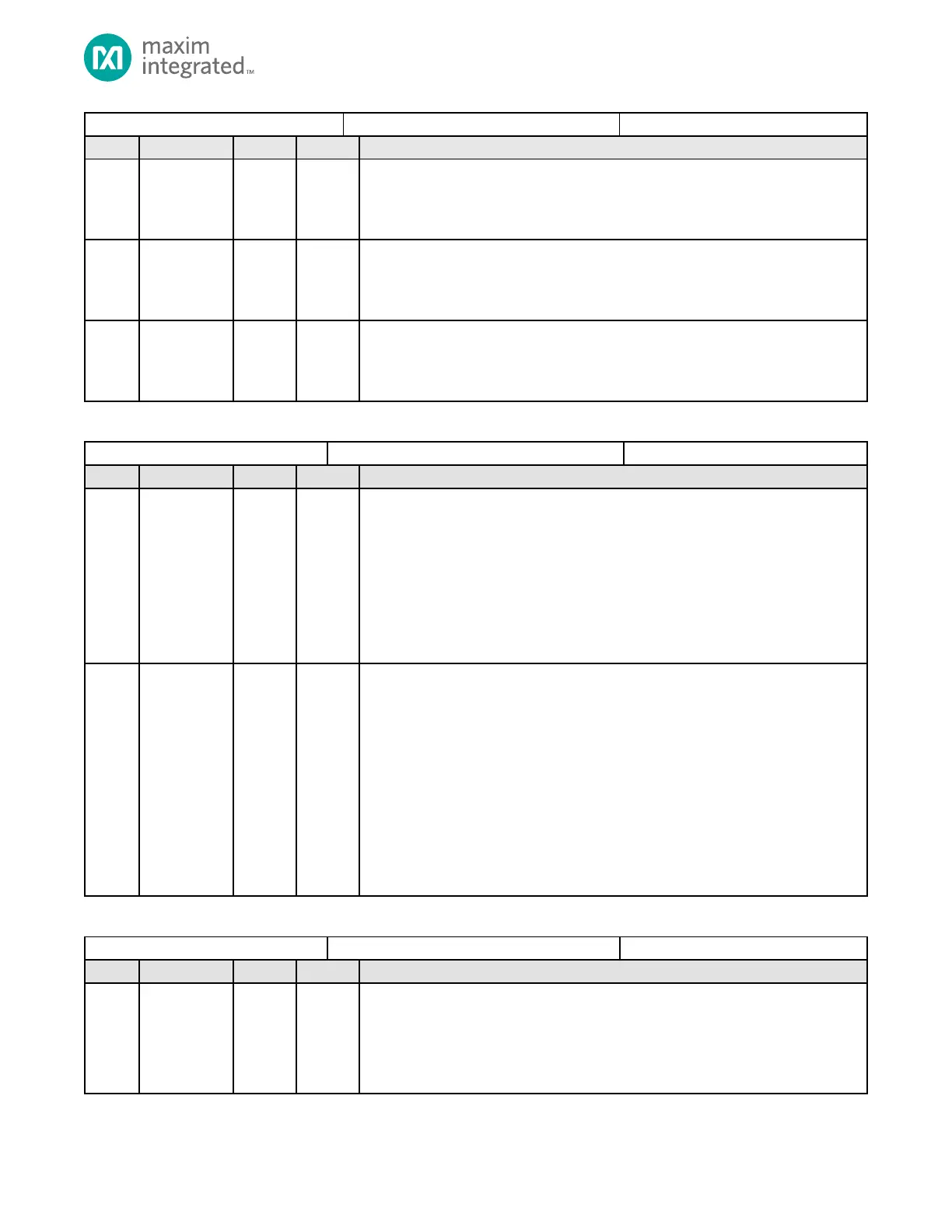

Table 17-9: Pulse Train Mode Bit Pattern Register

Pulse Train Mode Bit Pattern

Pulse Train Mode Bit Pattern

Write the repeating bit pattern that is shifted out, LSB first, when configured in pulse

train mode. Set the bit pattern length with the PTn_RATE_LENGTH.mode field.

Note: This register is ignored in Square Wave mode.

Note: 0x0000 0000and 0x0001 0000are invalid values for this register.

Loading...

Loading...