MAX32665-MAX32668 User Guide

Maxim Integrated Page 130 of 457

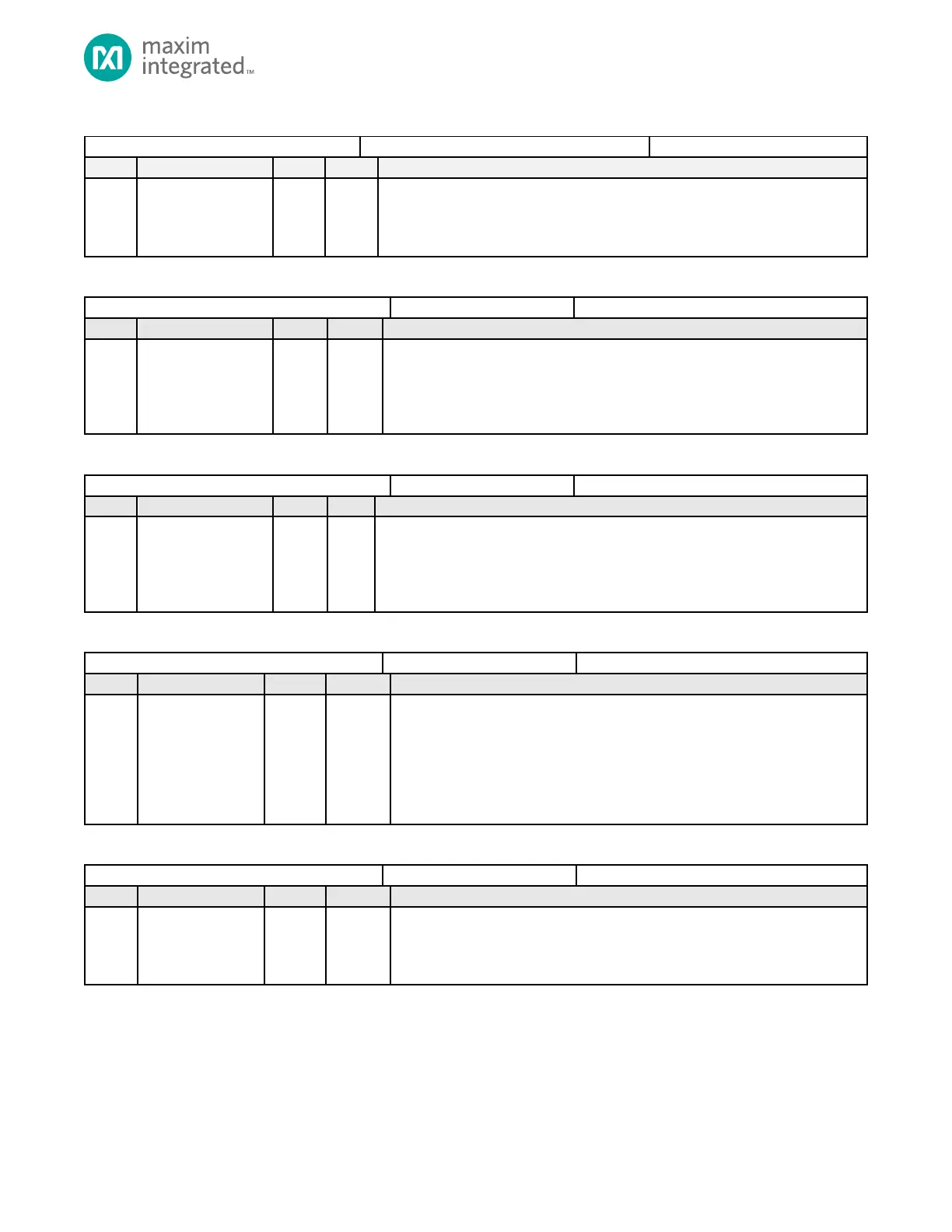

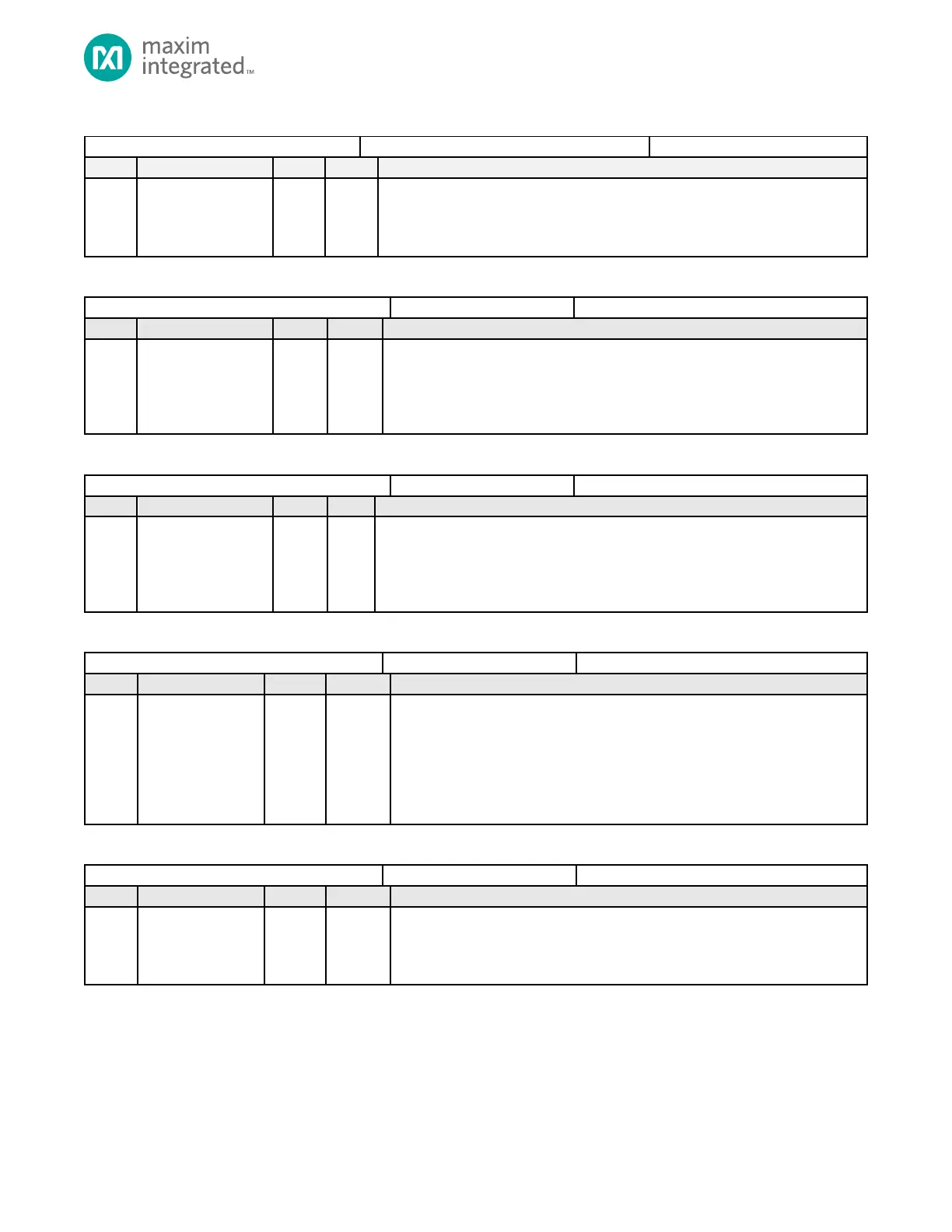

Table 6-27: GPIO Port n Wakeup Enable Register

GPIO Wakeup Enable

Enable the I/O as a wakeup from low power modes (SLEEP, DEEPSLEEP, BACKUP).

0: GPIO is not enabled as a wakeup source from low power modes.

1: GPIO is enabled as a wakeup source from low power modes.

Table 6-28: GPIO Port n Wakeup Enable Atomic Set Register

GPIO Port Wakeup Enable Atomic Set

GPIO Wakeup Enable Atomic Set

Writing 1 to one or more bits sets the corresponding bits in the GPIOn_WAKE_ENr

register.

0: No effect.

1: Corresponding bits in GPIOn_WAKE_EN register set to 1.

Table 6-29: GPIO Port n Wakeup Enable Clear Register

GPIO Port Wakeup Enable Atomic Clear

GPIO Wakeup Enable Atomic Clear

Writing 1 to one or more bits clears the corresponding bits in the GPIOn_WAKE_ENr

register.

0: No effect.

1: Corresponding bits in GPIOn_WAKE_EN register cleared to 0.

Table 6-30: GPIO Port n Interrupt Dual Edge Mode Register

GPIO Port n Pullup Pulldown Selection 0

GPIO Interrupt Dual-Edge Mode Select

Setting this bit triggers interrupts on both the rising and falling edges of the

corresponding GPIO if the associated GPIOn_INT_MODE bit is set to edge

triggered. The associated polarity (GPIOn_INT_POL) setting has no effect when this

bit is set.

0: No effect on interrupt generation.

1: Enable dual edge mode interrupts..

Table 6-31: GPIO Port n Pullup Pulldown Selection 0 Register

GPIO Port n Pullup Pulldown Selection 0

GPIO Pullup Pulldown Selection 0

Input mode configuration for the associated GPIO pin. Input mode selection and

the selection of a weak or strong pullup or weak or strong pulldown resistor are

described in Table 6-4.

Loading...

Loading...