MAX32665-MAX32668 User Guide

Maxim Integrated Page 143 of 457

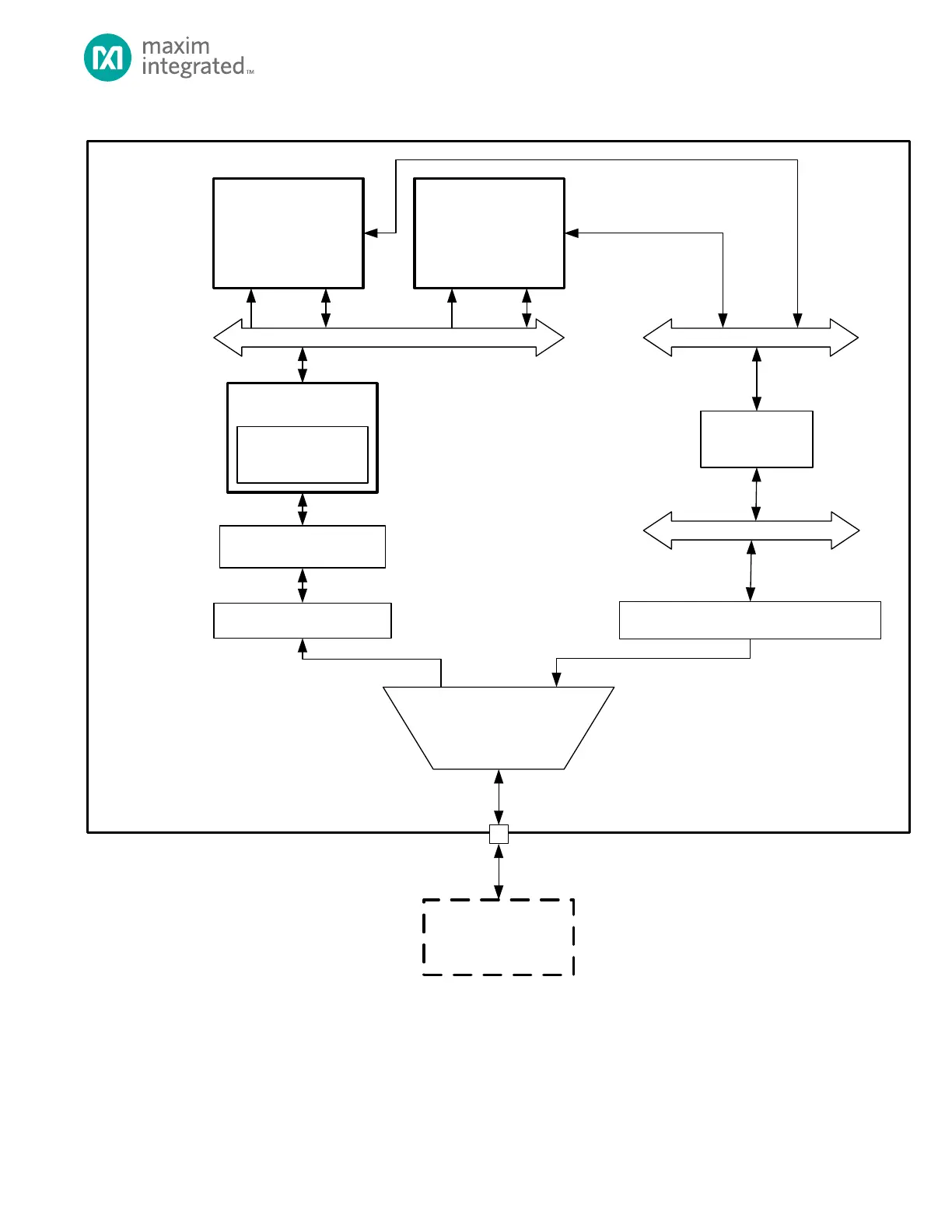

Figure 8-1. Simplified SPIXF Block Diagram

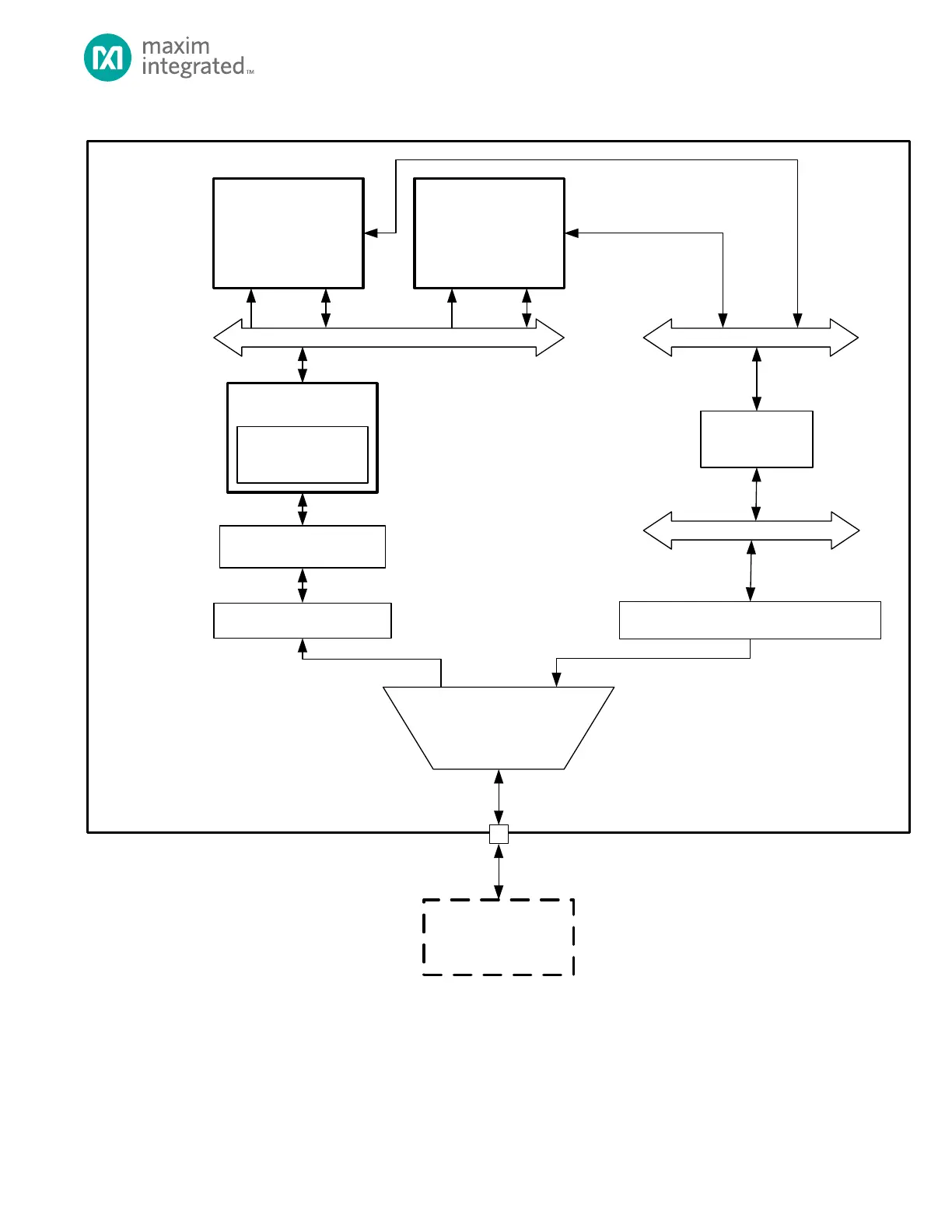

8.2.1 SPIXF Master Controller

The SPIXF Master Controller block (SPIXFC) shown in Figure 8-2 consists of transmit and receive shift registers (supported by

FIFOs) and a control unit. Communication and interface configuration are set up using the APB registers. It contains one

16×16 FIFO (Transmit FIFO) to support the transmit direction and one 32×8 FIFO (Receive FIFO) to support the receive

direction. These FIFOs are accessible to firmware using an AHB interface to support high-speed data transfers. New data is

moved automatically from the Transmit FIFO into the shift register at the start of every new SPI transfer as long as there is

Loading...

Loading...