MAX32665-MAX32668 User Guide

Maxim Integrated Page 128 of 457

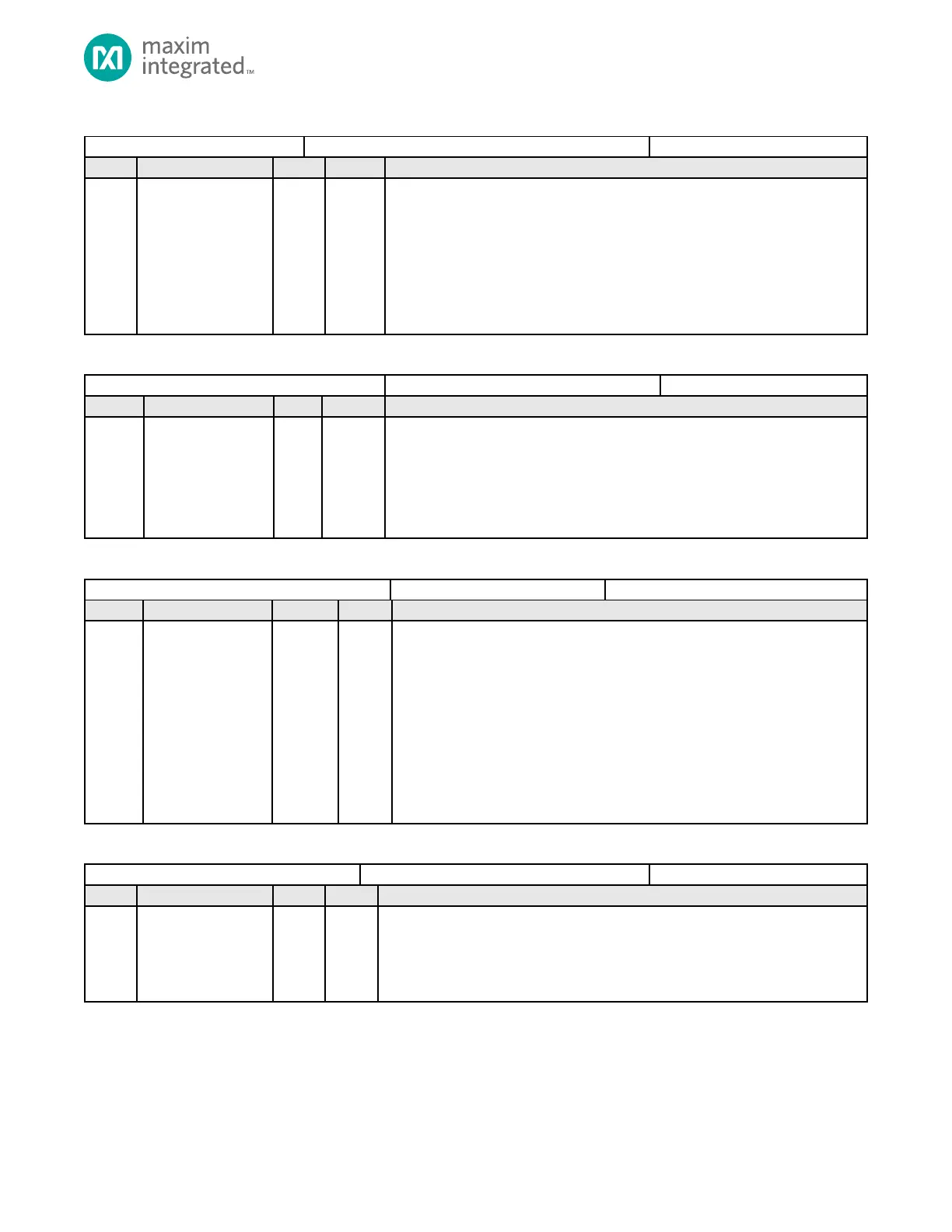

Table 6-18: GPIO Port n Input Register

GPIO Input

Returns the state of the input pin only if the corresponding bit in the GPIOn_IN_EN

register is set. The state is not affected by the pin’s configuration as an output or

alternate function.

0: Input pin low

1: Input pin high.

Note: This bit is ignored if the corresponding bit position in the GPIOn_OUT_EN

register and GPIOn_OUT_EN register is not set..

Table 6-19: GPIO Port n Interrupt Mode Register

GPIO Port n Interrupt Mode

GPIO Interrupt Mode

Selects interrupt mode for the corresponding GPIO pin.

0: Level triggered interrupt.

1: Edge triggered interrupt.

Note: This bit has no effect unless the corresponding bit in the GPIOn_INT_EN

register is set.

Table 6-20: GPIO Port n Interrupt Polarity Register

GPIO Port n Interrupt Polarity

GPIO Interrupt Polarity

Interrupt polarity selection bit for the corresponding GPIO pin.

Level triggered mode (GPIOn_INT_MODE = 0):

0: Input low (logic 0) triggers interrupt.

1: Input high (logic 1) triggers interrupt.

Edge triggered mode (GPIOn_INT_MODE = 1):

0: Falling edge triggers interrupt

1: Rising edge triggers interrupt.

Note: This bit has no effect unless the corresponding bit in the GPIOn_INT_EN

register is set.

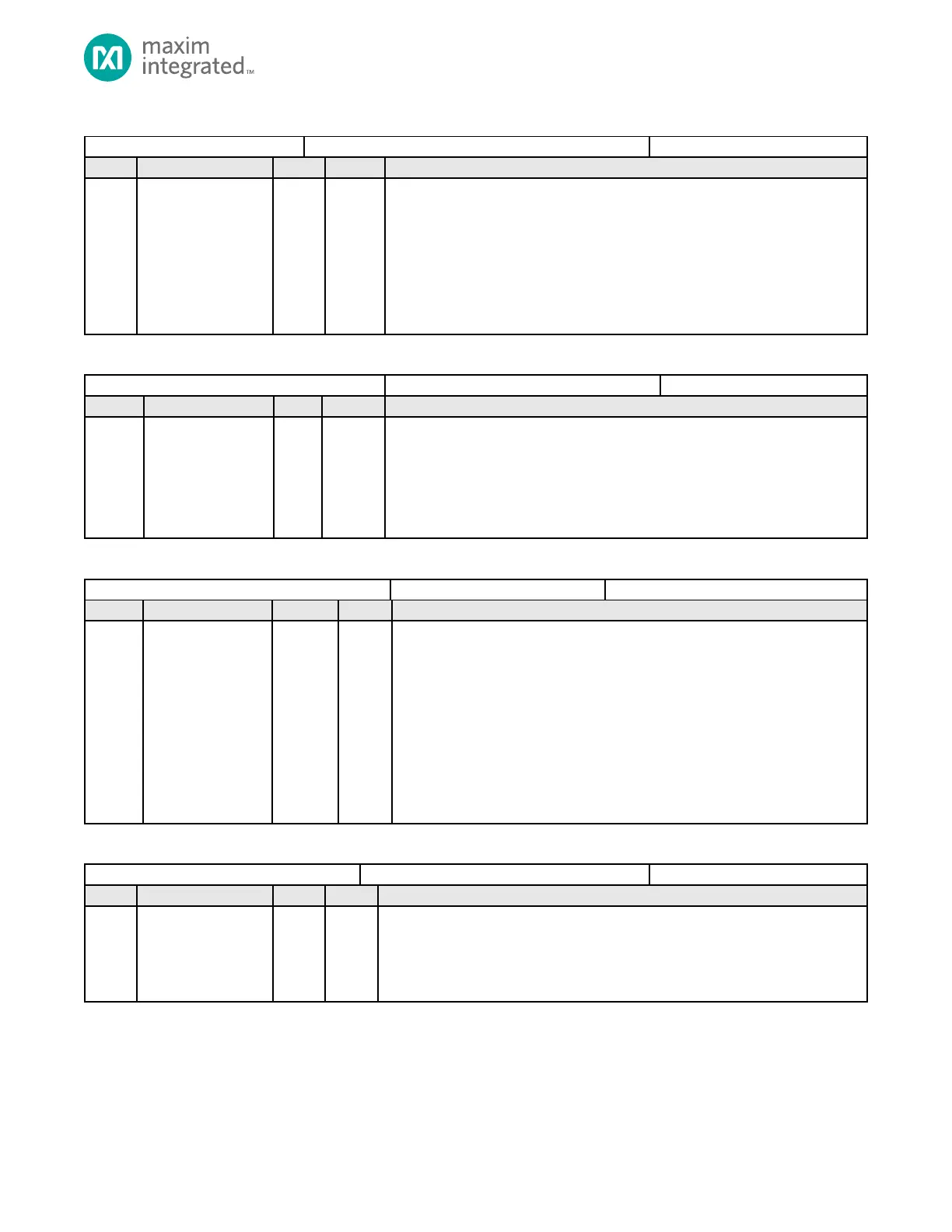

Table 6-21: GPIO Port n Input Enable Register

GPIO Input Enable

Connects the corresponding input pad to the specified input pin for reading the pin

state using the GPIOn_IN register.

0: Input not connected.

1: Input pin connected to the pad for reading via GPIOn_IN register.

Loading...

Loading...