MAX32665-MAX32668 User Guide

Maxim Integrated Page 115 of 457

5. Interrupts and Exceptions

Interrupts and exceptions are managed by the Arm Cortex-M4 with FPU Nested Vector Interrupt Controller (NVIC). The

NVIC handles the interrupts, exceptions, priorities and masking. Table 5-1 details the MAX32665—MAX32668 interrupt

vector table and describes each exception and interrupt.

5.1 Features

• 59 maskable interrupts not including the 15 system exceptions of the Arm Cortex-M4 with FPU

• 8 programmable priority levels

• Nested exception and interrupt support

• Interrupt masking

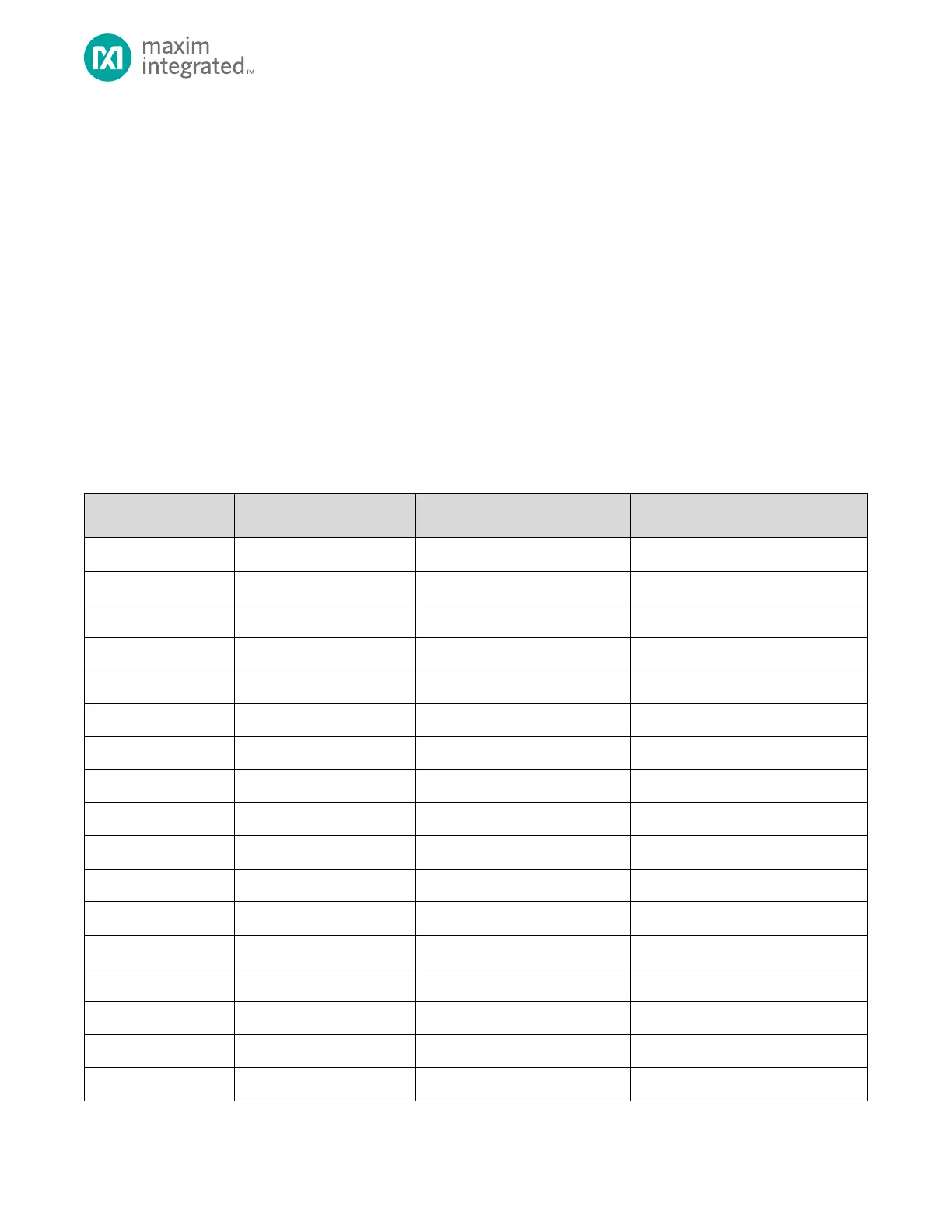

5.2 Interrupt Vector Table

Table 5-1 lists the interrupt and exception table for the MAX32665—MAX32668. There are 95 interrupt entries for the

MAX32665—MAX32668, including reserved for future use interrupt place holders. Including the 15 system exceptions for

the Arm Cortex-M4 with FPU, the total number of entries is 110.

Table 5-1: MAX32665—MAX32668 Interrupt Vector Table

Loading...

Loading...