MAX32665-MAX32668 User Guide

Maxim Integrated Page 448 of 457

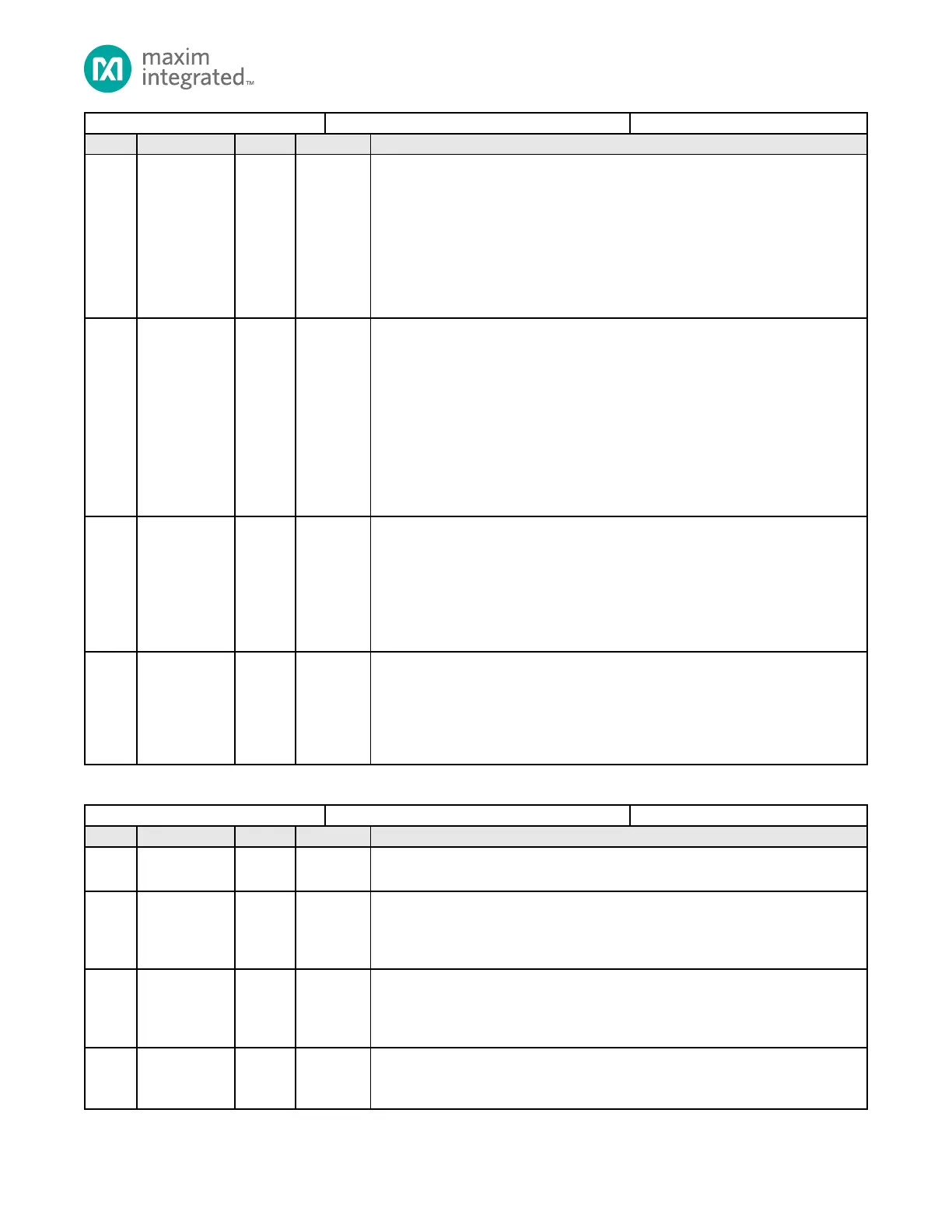

Last Message Bit

This bit is set along with the HASH MSG_SZ_3:0 register prior to hashing the last 512

or 1024-bit block of the message data. It allows automatic preprocessing of the last

message padding, which includes the trailing bit 1 followed by the respective number

of zero bits for the last block size and the message length represented in bytes. The bit

is automatically cleared at the same time the CRYPTO_CTRL.hsh_done is set,

designating the completion of the last message.

0: No effect

1: Last message data

Hash Function Selection.

Select the hash mode algorithm. Clear these bits before starting any other operation

of the cryptographic accelerator.

0b000: Hash disabled

0b001: SHA-1

0b010: SHA-224

0b011: SHA-256

0b100: SHA-384

0b101: SHA-512

0b110: Reserved

0b111: Reserved

XOR IV and Cipher Block

Useful when calculating HMAC to XOR the input pad and output pad. Use the feature

to Load Key from CMDA.

This bit is automatically cleared by hardware after the DMA completes loading the

key. When the DMA operation is done, it sets the appropriate CMDA Done flag.

0: No XOR

1: XOR input with IV

Initialize

Load HASH_DIGEST_0 HASH_DIGEST_[15:0] with the initial hash values based on the

message digest size the initial hash values corresponding to the selected hash

function.

0: NOP

1: Initialize hash values

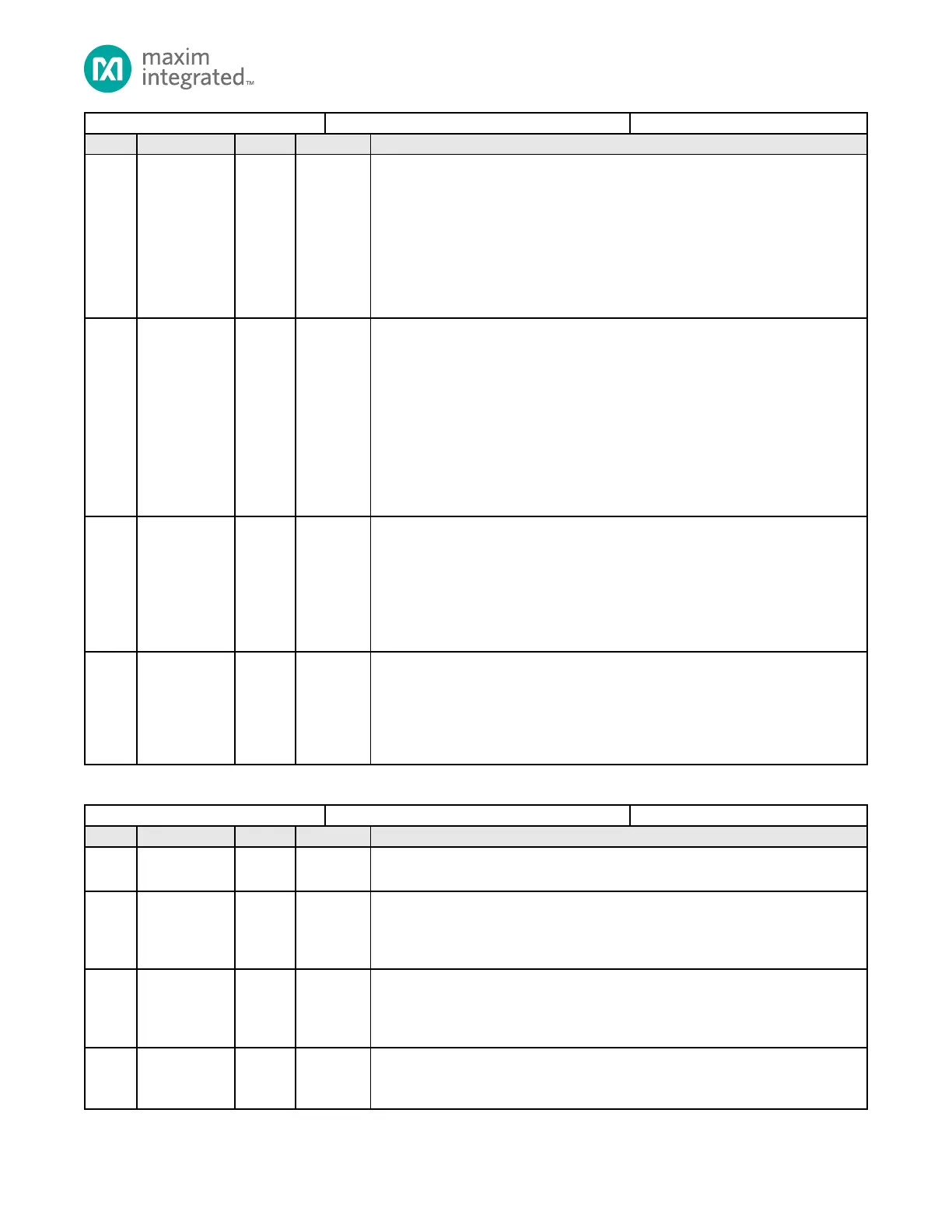

Table 23-11: CRC Control Register

Reserved for Future Use

Do not modify this field from its default value.

Hamming Reset

Reset the Hamming code ECC generator for the next block.

0: NOP

1: Reset Hamming Register

Hamming Code Enable

Enable Hamming code calculation.

0: Hamming disabled

1: Hamming enabled

Entropy Enable

This feature is not implemented in this device. Do not change this bit from its default

value.

Loading...

Loading...