MAX32665-MAX32668 User Guide

Maxim Integrated Page 158 of 457

8.2.1.4 SPIXF Master Controller FIFO Registers

See Table 3-2: AHB Peripheral Base Address Map for the SPIXF Master Controller FIFO Peripheral Base Address.

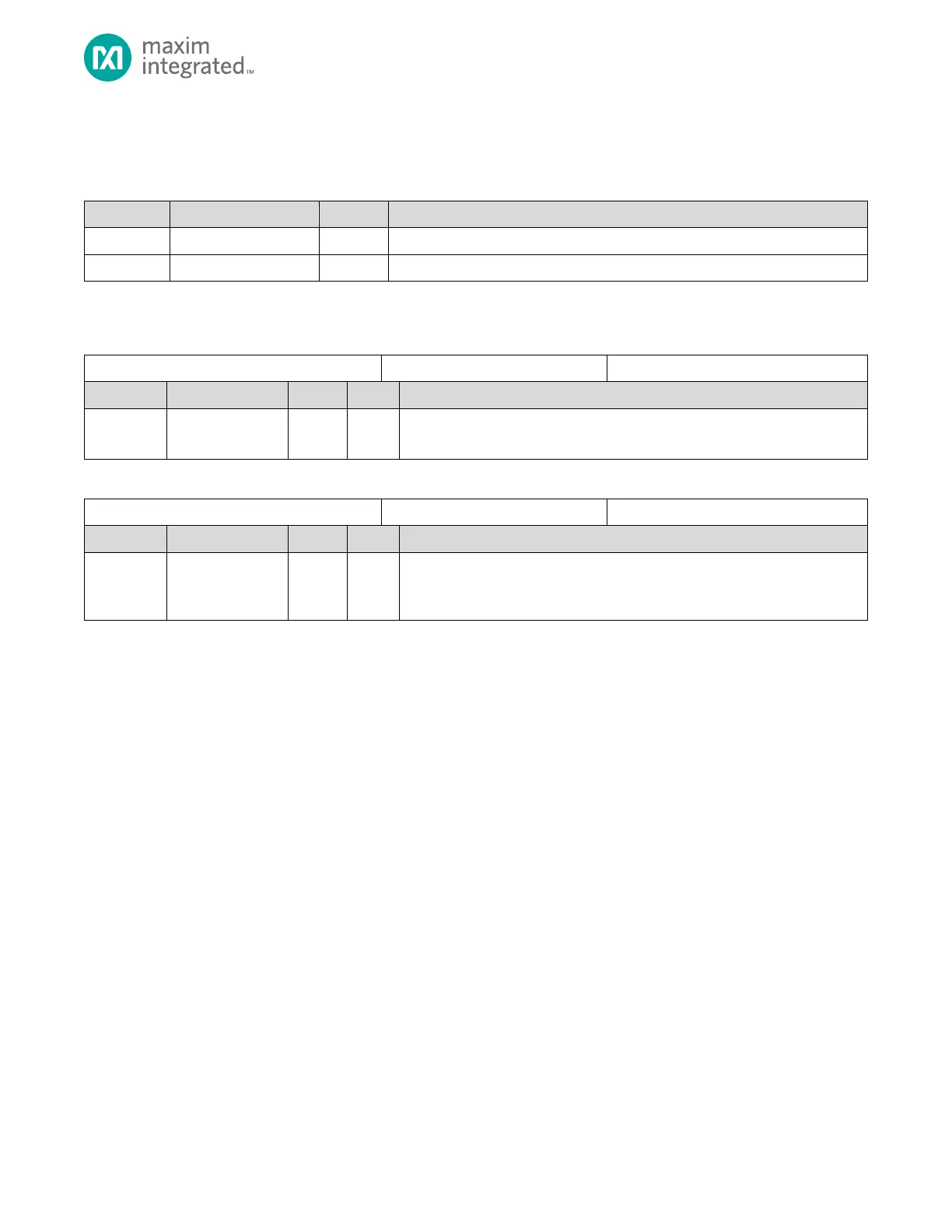

Table 8-12. SPIXF Master Controller FIFO Register Offsets, Names, Access and Description

SPIXF Master Controller TX FIFO Register

SPIXF Master Controller RX FIFO Register

8.2.1.5 SPIXF Master Controller FIFO Register Details

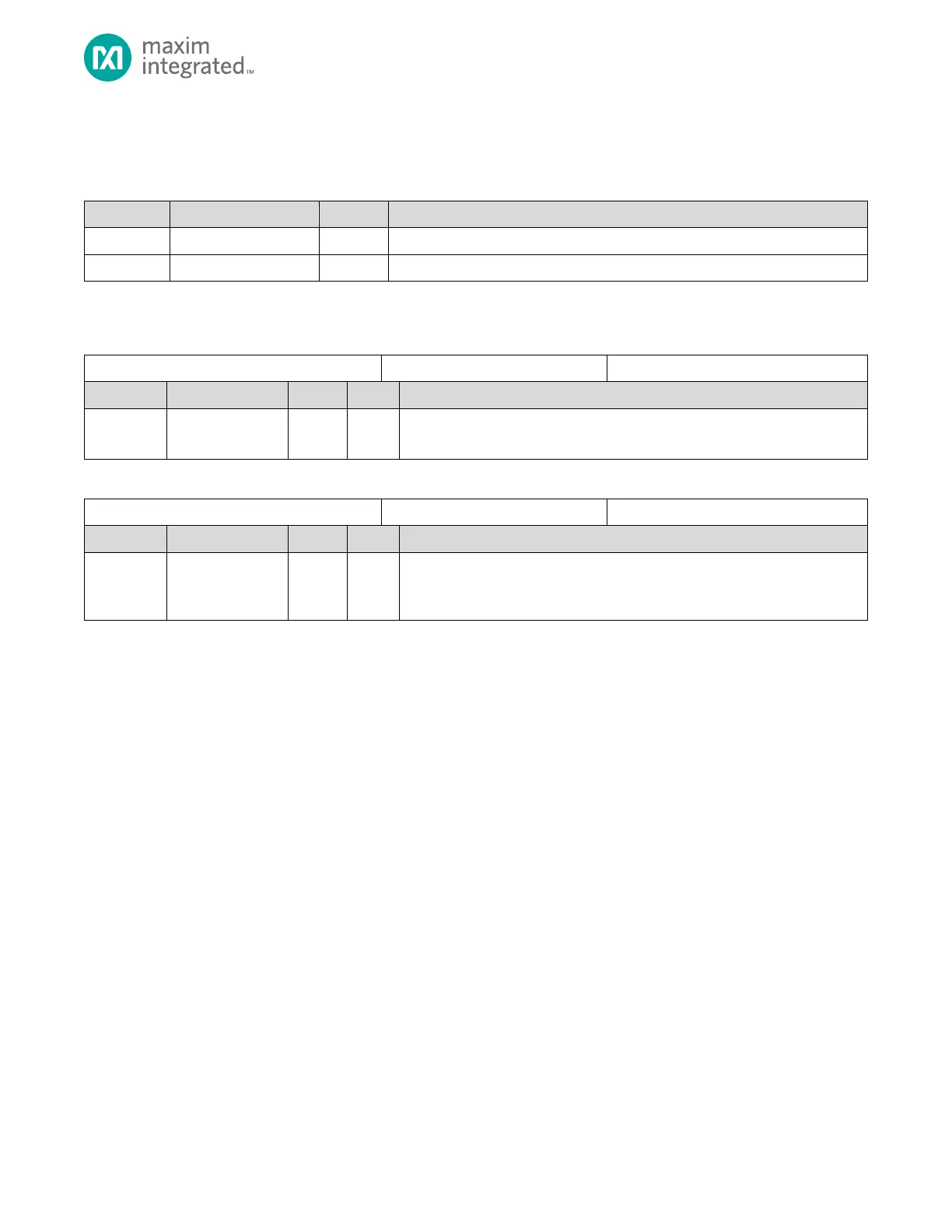

Table 8-13. SPIXF Master Controller TX FIFO Register

SPIXF Master Controller TX FIFO Register

TX FIFO

Writes to this register are put into the TX FIFO for the SPIXF Master Controller.

Table 8-14. SPIXF Master Controller TX FIFO Register

SPIXF Master Controller RX FIFO Register

RX FIFO

Reads from this register return the data from the SPIXF Master Controller RX

FIFO.

8.2.2 SPIXF Master

The SPIXF Master (SPIXFM) is an AHB slave interface that is driven by a 16KB Unified Instruction and Constant cache to

support cache operation. The AHB slave supports either instruction execution or fetching of data from external SPI flash.

This interface is accessible to firmware using an AHB interface to support high-speed data transfer. The address for SPI flash

access is determined by the AHB access and is mapped from address 0x0800 0000 to 0x0FFF FFFF for a total addressable

space of 128MB.

The command used to transfer SPI flash data is configured using firmware. Then, the access to SPI flash space (either code

execution or data) may be performed by firmware. The AHB transaction initiated by the firmware provides address and

other transaction critical parameters to control the data transfer from the external SPI flash.

You should exercise care in choosing the correct configuration and command to support the speed of data transfer. The

SPIXF Master provides SCK periods as fast as the AHB clock speed divided by two. The external SPI flash configuration to

support data transfer rates must be performed by the SPIXF Master Controller.

Loading...

Loading...