MAX32665-MAX32668 User Guide

Maxim Integrated Page 419 of 457

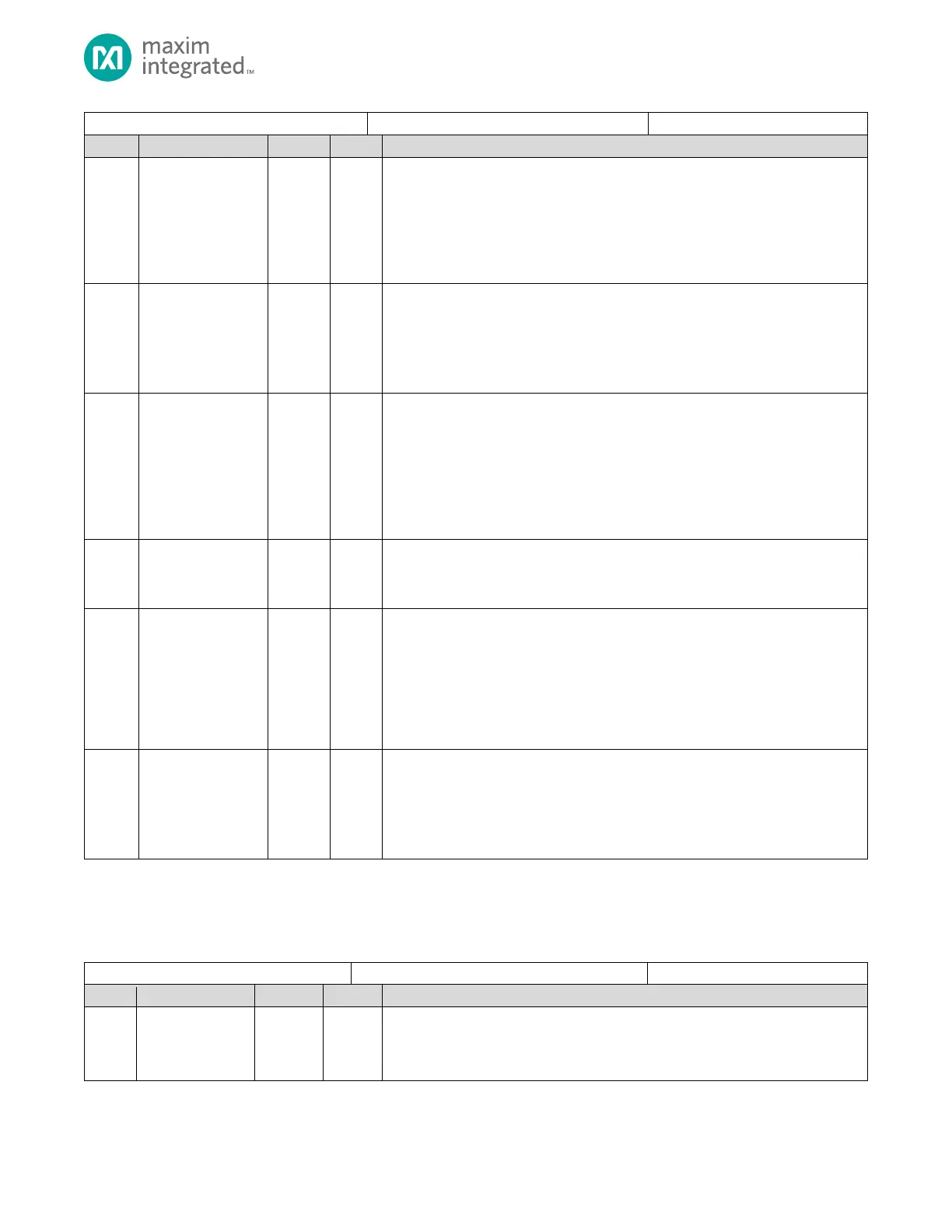

USBHS Endpoint 0 Control Status

Send EP0 STALL Handshake

Write a 1 to this bit to terminate the current Control Transaction by sending a

STALL handshake.

Automatically cleared after being set.

Note: This behavior is different from the sendstall bits associated with IN/OUT

endpoints.

Read Setup End Status

Automatically set when a Control Transaction ends before the dataend bit has been

set by firmware.

An interrupt is generated when this bit is set.

Write a 1 to servicedsetupend (above) to clear.

Control Transaction Data End

Write a 1 to this bit after firmware completes any of the following three

transactions:

1) Set inpktrdy = 1 for the last data packet.

2) Set inpktrdy = 1 for a zero-length data packet.

3) Clear outpktrdy = 0 after unloading the last data packet.

Note: Automatically cleared after being set.

Read EP0 STALL Handshake Sent Status

Automatically set when a STALL handshake is transmitted.

Write a 0 to clear.

EP0 IN Packet Ready

Set this bit to indicate a packet is ready to transmit from the IN FIFO. Hardware

automatically clears this bit when the packet transmit is complete.

0: Packet was transmitted or no packet transmit pending. Read only.

1: Write a 1 after writing a data packet to the IN FIFO to indicate the EP0 IN

packet is ready.

Note: An interrupt is generated when this bit is cleared.

EP0 OUT Packet Ready Status

Automatically set when a data packet is received in the OUT FIFO.

An interrupt is generated when this bit is set.

Write a 1 to the servicedoutpktrdy bit (above) to clear after the packet is unloaded

from the OUT FIFO.

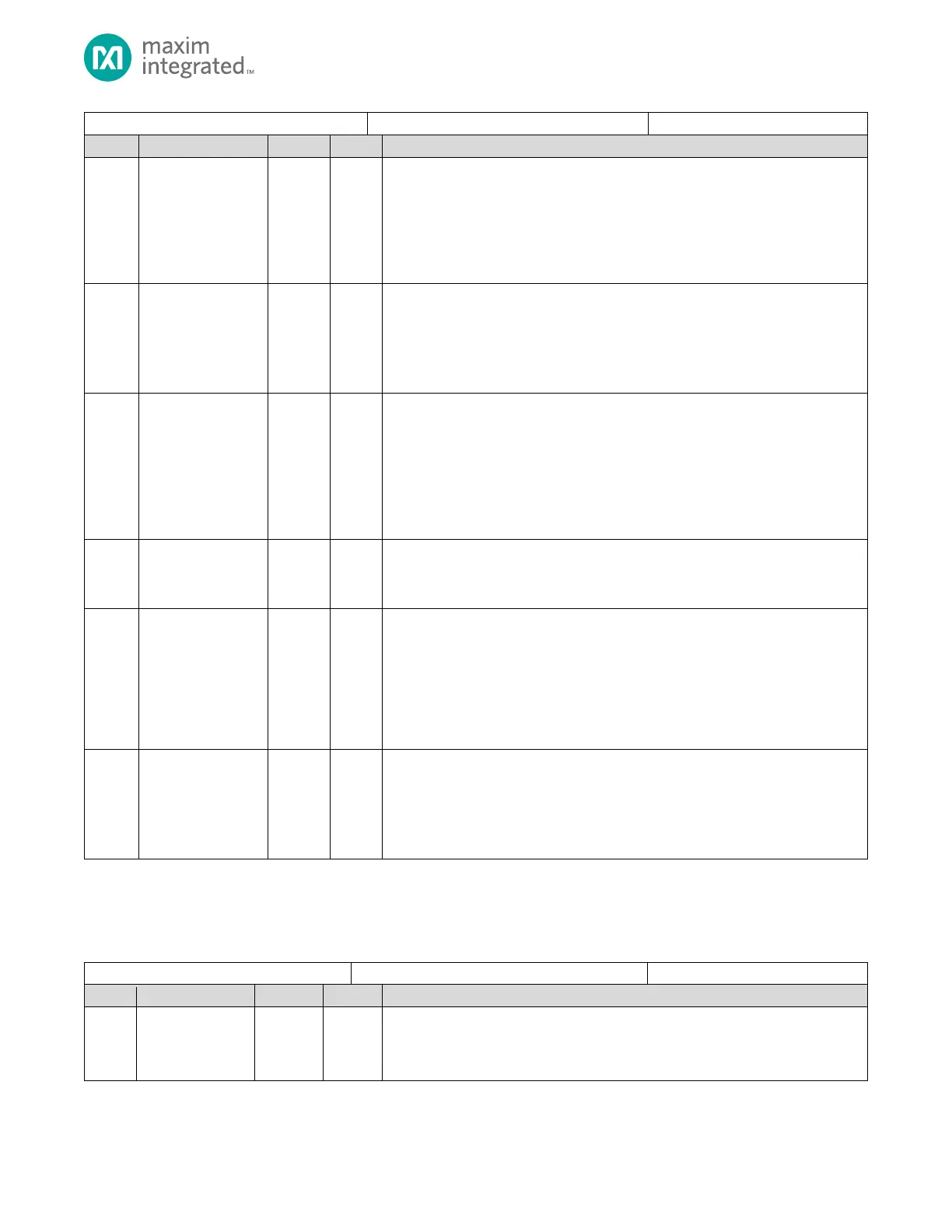

21.12.6 USBHS IN Endpoint Upper Control Registers

Endpoint 1 to 11 have a memory mapped version of this register selected using the USBHS_INDEX register.

Table 21-21: USBHS IN Endpoint Upper Control Register

USBHS IN Endpoint Upper Control

Auto Set inpktrdy

0: USBHS_INCSRL.inpktrdy must be set by firmware

1: USBHS_INCSRL.inpktrdy is automatically set when data that is of the maximum

packet size specified in the USBHS_INMAXP register is loaded into the IN FIFO.

Loading...

Loading...