MAX32665-MAX32668 User Guide

Maxim Integrated Page 203 of 457

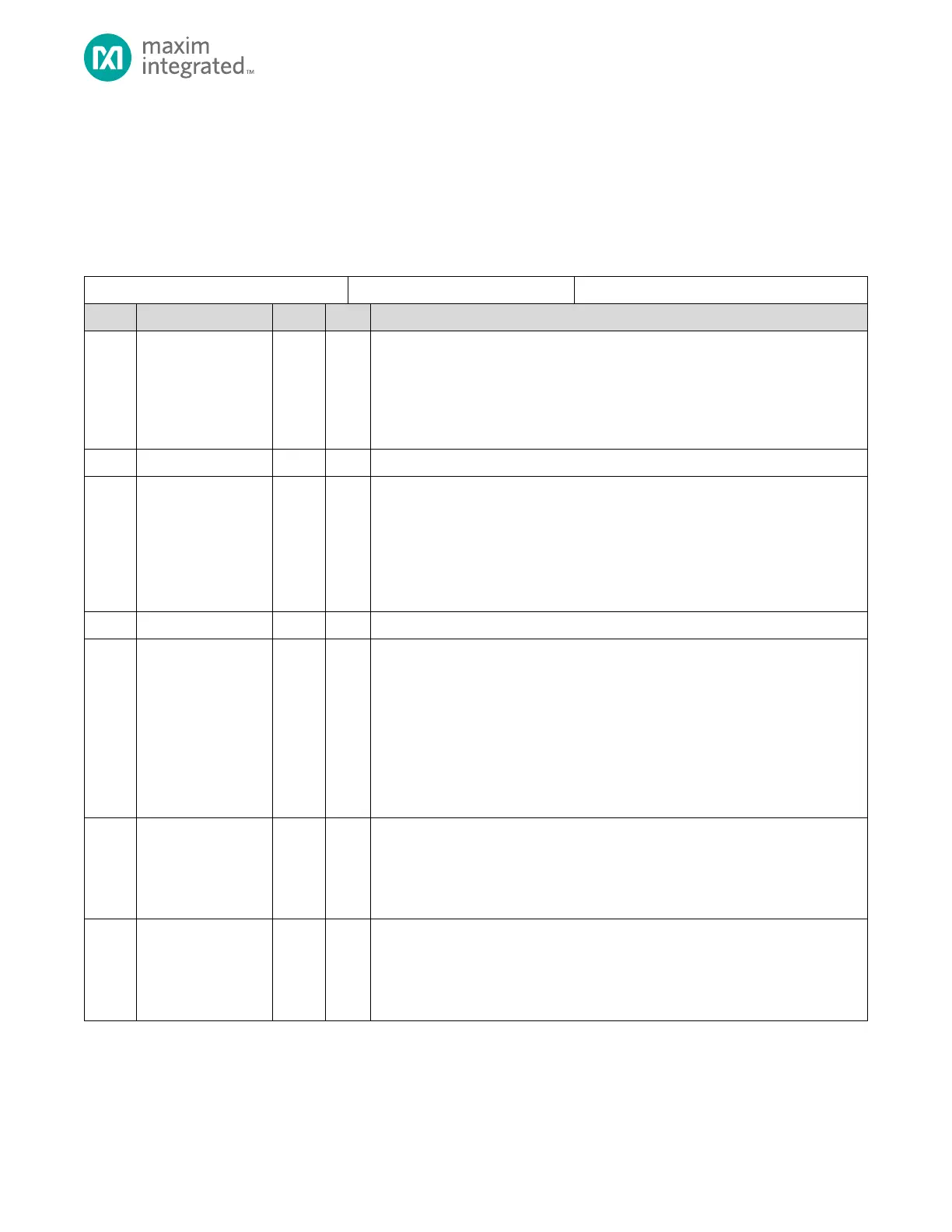

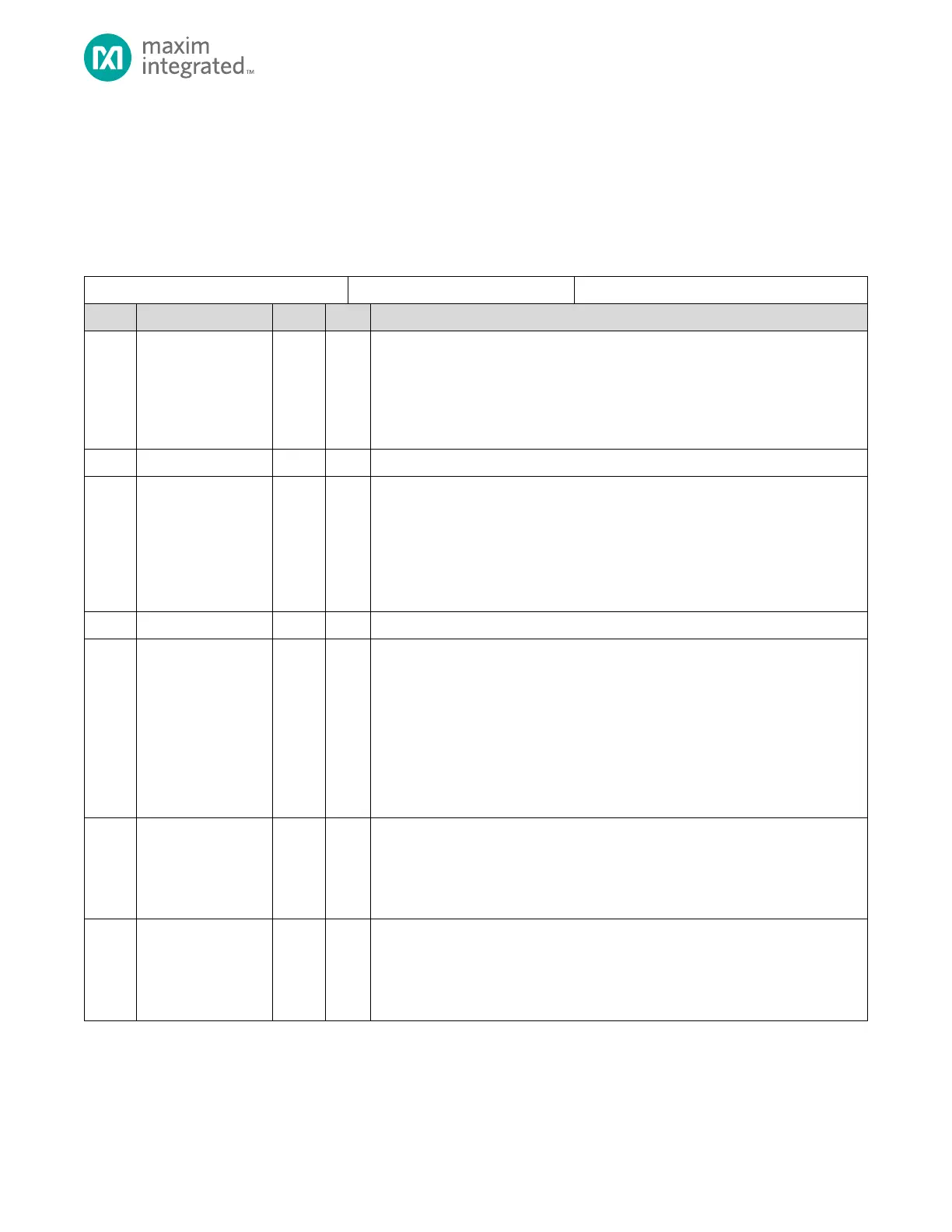

8.5.6.1 Normal Interrupt Status Register

The Normal Interrupt Status Enable affects reads of this register, but Normal Interrupt Signal Enable does not. An interrupt

is generated when the Normal Interrupt Signal Enable is enabled, and at least one of the status bits is set to 1. Writing 1 to a

bit of the RW1C attribute clears it. Writing 0 keeps the bit unchanged. Writing 1 to a bit of the ROC attribute keeps the bit

unchanged. You can clear more than one status with a single register write. The Card Interrupt (SDHC_INT_STAT.card_intr)

is cleared when the card stops asserting the interrupt after the Card Driver services the interrupt condition.

Table 8-73: SDHC Normal Interrupt Status Register

Normal Interrupt Status Register

Error Interrupt

If any of the bits in the Error Interrupt Status register are set, then this bit is set.

Therefore, the Host Driver can efficiently test for an error by checking this bit first.

This bit is read only.

1: Error

0: No Error

Re-Tuning Event

This status is set if the Re-Tuning Request bit in the Present State register changes

from 0 to 1. The SDHC requests the Host Driver to perform re-tuning for the next data

transfer. However, you can complete the current data transfer (not large block count)

without re-tuning.

1: Perform re-tuning before the next data transfer

0: Re-tuning is not required

Card Interrupt

In one-bit mode, the SDHC detects the Card Interrupt without the SD Clock to support

wakeup. In four-bit mode, the card interrupt signal is sampled during the interrupt

cycle resulting in a delay between the interrupt signal from the memory card and the

interrupt signal to the host driver.

1: Generate Card Interrupt

0: No Card Interrupt

Note: Writing a 1 to this bit does not clear this bit. It is cleared by resetting the

SDHC_INT_EN.card_int flag.

Card Removal

Set if the Card Inserted field in the Present State register

(SDHC_PRESENT.card_inserted) changes from 1 to 0.

1: Card removed

0: Card state stable or hardware debouncing

Card Inserted

Set if the Card Inserted field in the Present State register

(SDHC_PRESENT.card_inserted) changes from 0 to 1.

1: Card inserted

0: Card state stable or hardware debouncing

Loading...

Loading...