MAX32665-MAX32668 User Guide

Maxim Integrated Page 206 of 457

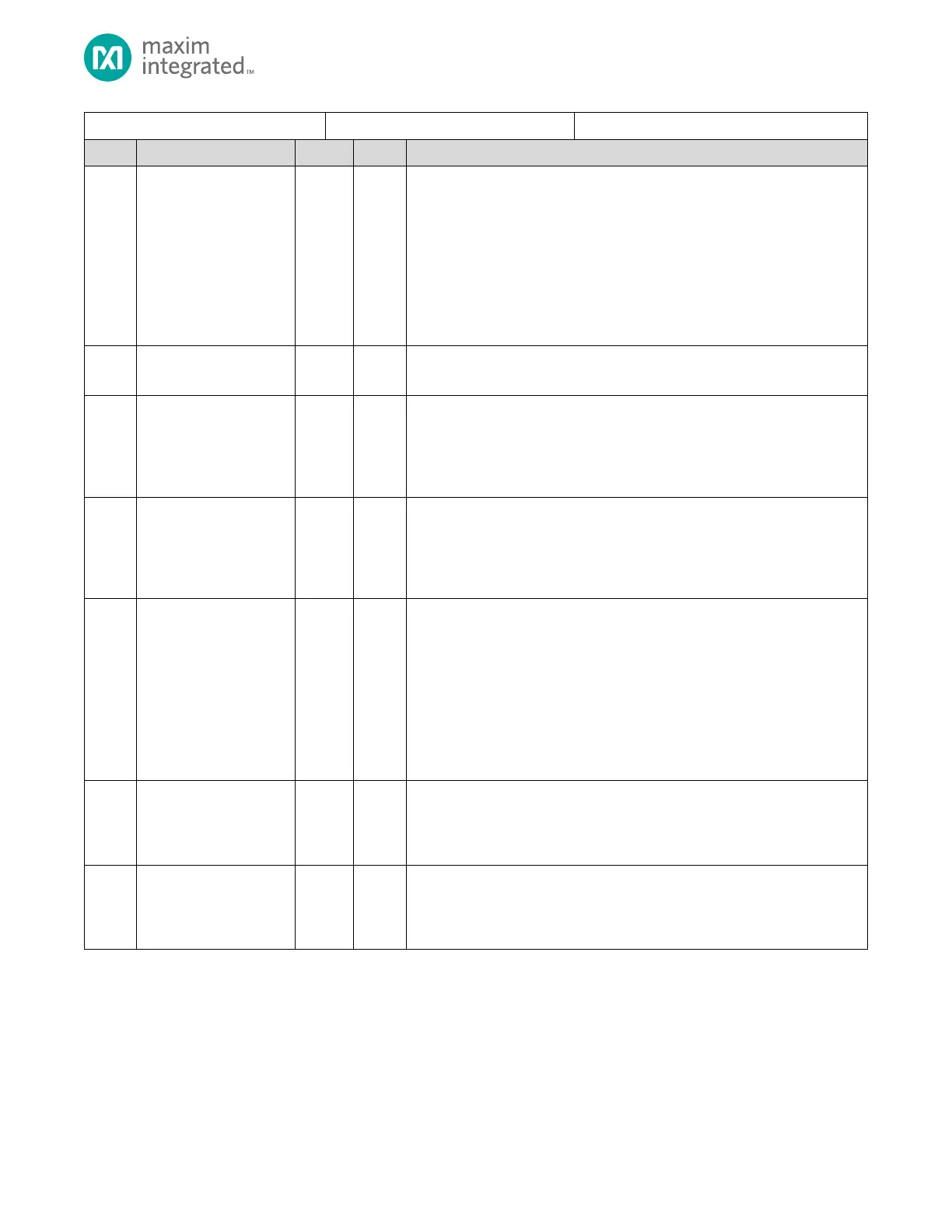

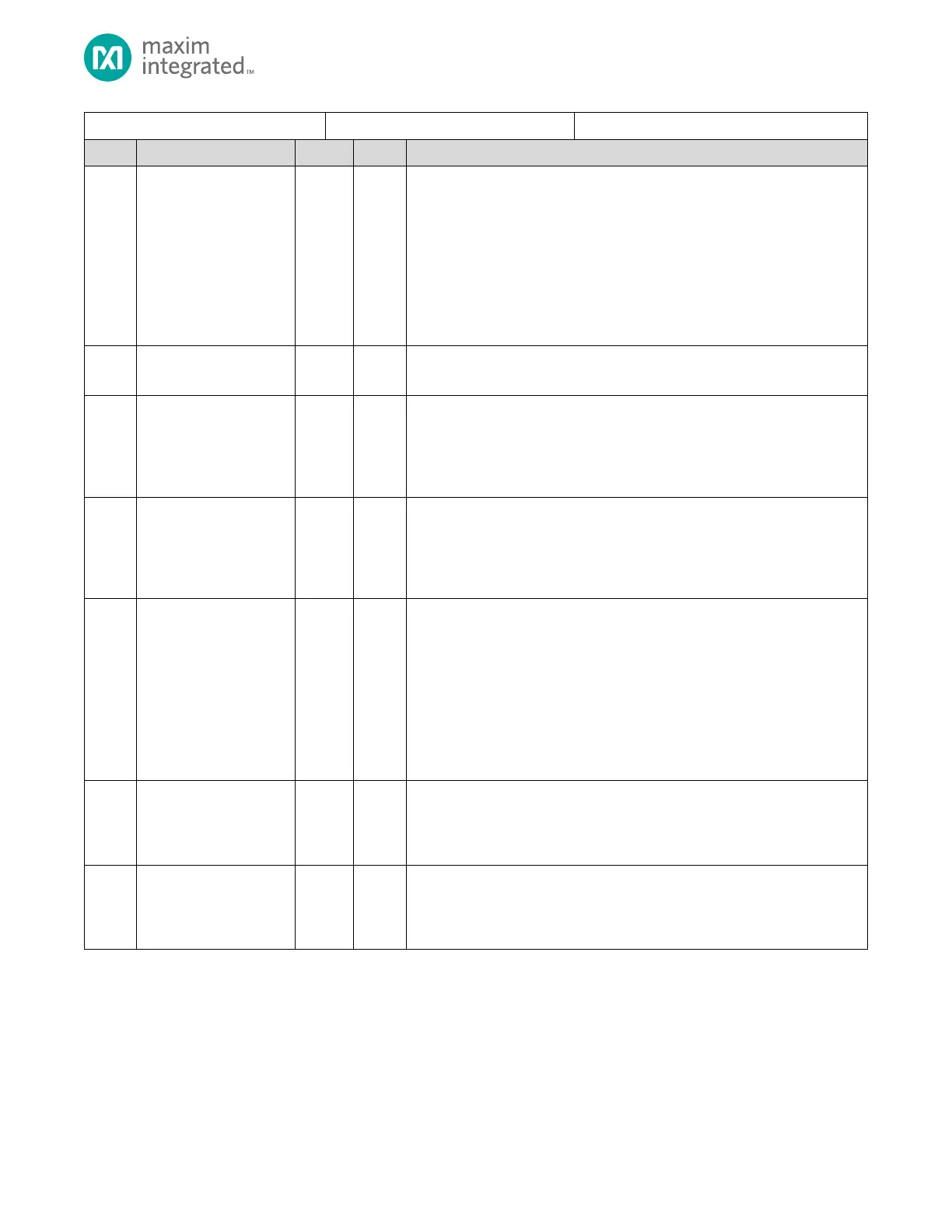

Error Interrupt Status Register

Auto CMD Error

Auto CMD12 and Auto CMD23 use this error status. This bit is set when

detecting that one of the bits D00-D04 in Auto CMD Error Status

(SDHC_AUTO_CMD_ER) register changed from a 0 to a 1.

1: Error

0: No error

Note: For Auto CMD12, this bit is set to 1 not only when an error occurs in Auto

CMD12, but also when Auto CMD12 is not executed due to a previous

command error.

Current Limit Error

Not supported on MAX32665—MAX32668

Data End Bit Error

Set if a 0 is detected at the end bit position of read data that uses the DAT line

or the end-bit position of the CRC status.

1: Error

0: No error

Data CRC Error

Set when a CRC error is detected when receiving read data that uses the DAT

line or when detecting a Write CRC status with a value other than 010.

1: Error

0: No error

Data Timeout Error

Set for any of the following timeout conditions:

• Busy timeout for R1b and R5b response types. See Table 8-53 for more

information about response types.

• Busy timeout after Write CRC status

• Write CRC status Timeout

• Read Data Timeout

1: Error

0: No error

Command Index Error

Set if a Command Index error is detected in the Command Response.

1: Error

0: No error

Command End Bit Error

Set if the end bit of a Command Response is 0.

1: Error

0: No error

Loading...

Loading...