MAX32665-MAX32668 User Guide

Maxim Integrated Page 194 of 457

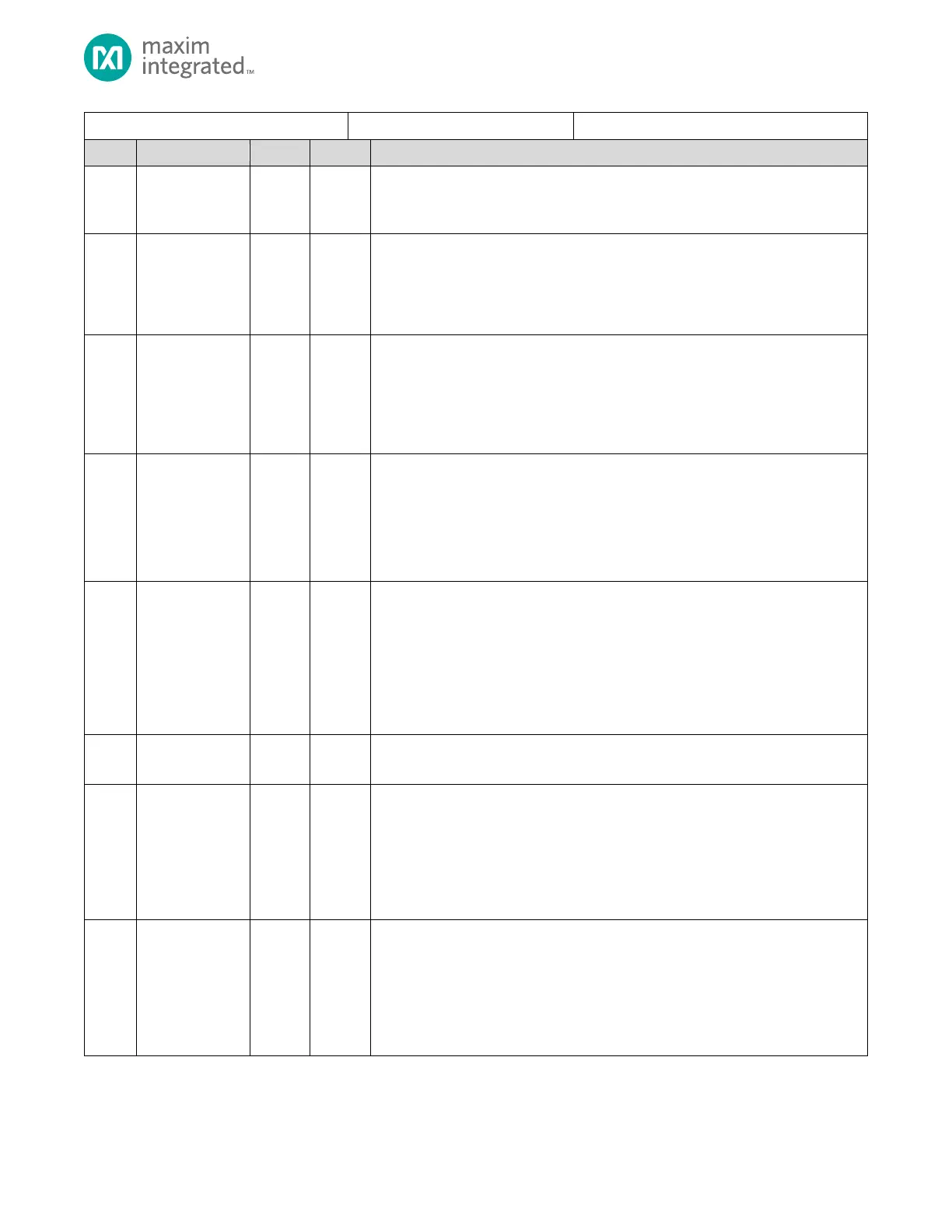

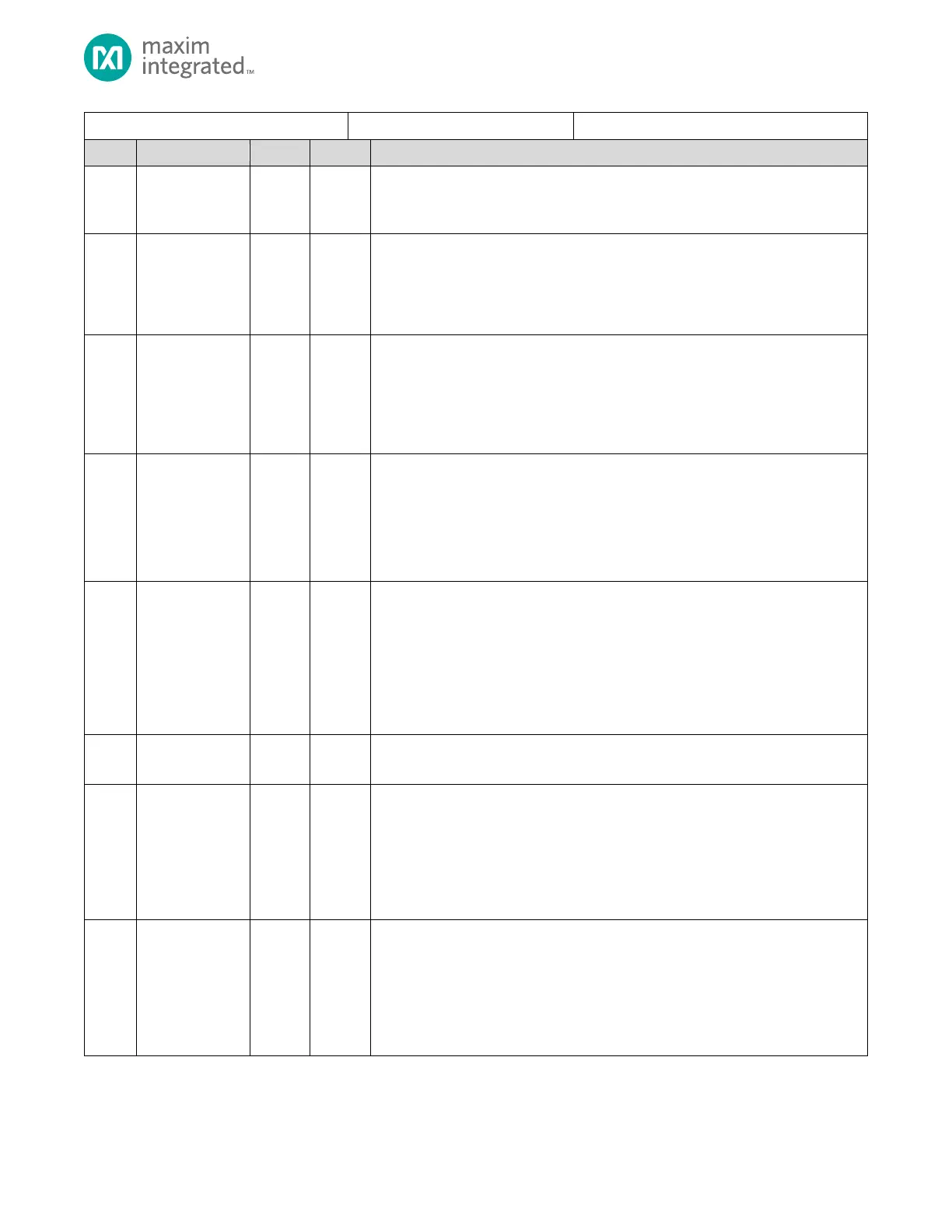

SDHC_DAT[3:0] Line Signal Level

Indicates the DAT line level for error recovery and debugging. Use to detect the busy

signal level as indicated on SDHC_DAT[0].

Write Protect Switch Pin Level

The write protect switch is supported for memory and combo cards. This bit reflects

the state of the SDHC_WP pin.

1: Write enabled (SDHC_WP = 1)

0: Write protected (SDHC_WP = 0)

Card Detect Pin Level

This bit reflects the inverted state of the SDHC_CDN pin. Debouncing is not

performed on this bit. When Card State Stable is set to 1, this bit might be valid, but is

not guaranteed. To use this bit, the card driver must debounce the bit.

1: Card present (SDHC_CDN = 0)

0: No card present (SDHC_CDN = 1)

Card State Stable

Used for debugging only. If this bit reads 0, the SDHC_CDN pin level is not stable. If

this bit reads 1, the SDHC_CDN pin level is stable.

1: No card or card inserted

0: Reset or debouncing

Note: This bit is not valid unless the SDHC_PRESENT.card_inserted bit reads 1.

Card Inserted

Indicates if a card is inserted. This signal is debounced by the SDHC hardware. A

change in state from 0 to 1 on this bit generates an SDHC_IRQ with the

SDHC_INT_STAT.card_insertion flag set. Conversely, a transition of this bit from a 1 to

a 0 generates an SDHC_IRQ interrupt with the SDHC_INT_STAT.card_removal field

set.

1: Card Inserted

0: Reset, debouncing, or no card inserted

Reserved for Future Use

Do not modify this field.

Buffer Read Status

If this bit reads 1, then data is available in the buffer for non-DMA transfers. This bit is

cleared when all available block data is read from the buffer. This bit transitions from

0 to 1 when block data is ready in the buffer resulting in a SDHC_IRQ interrupt, if

enabled, with the SDHC_INT_STAT.buffer_rd_ready flag set.

1: Read data available

0: No data to read

Buffer Write Status

If this bit reads 1, then space is available in the buffer for write data. This bit is

cleared when no space is available in the buffer. This bit transitions from a 0 to a 1

when top-of-block data is written to the buffer, resulting in a SDHC_IRQ interrupt, if

enabled, with the SDHC_INT_STAT.buffer_wr_ready flag set.

1: Space available in the buffer for write data

0: No space available in the buffer for write data

Loading...

Loading...