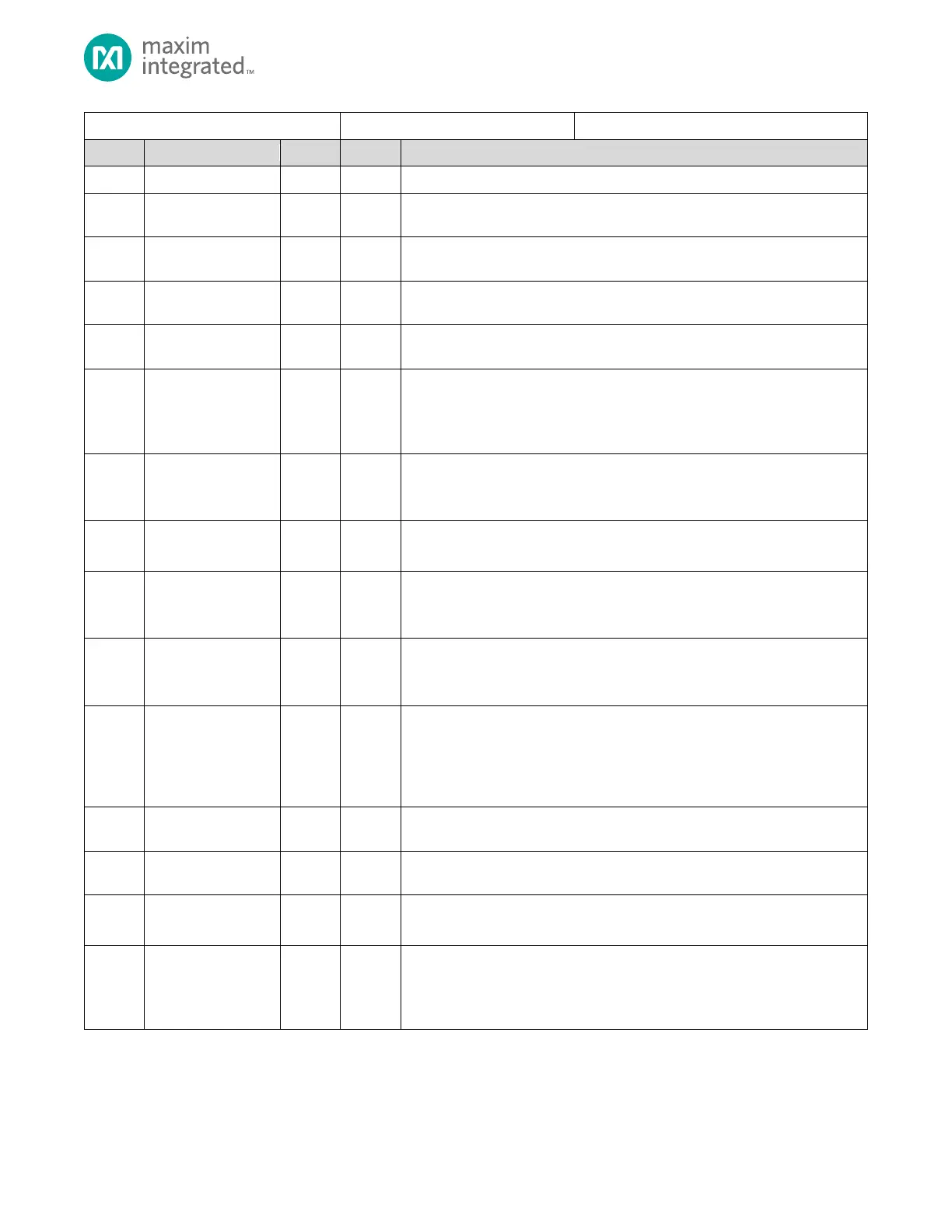

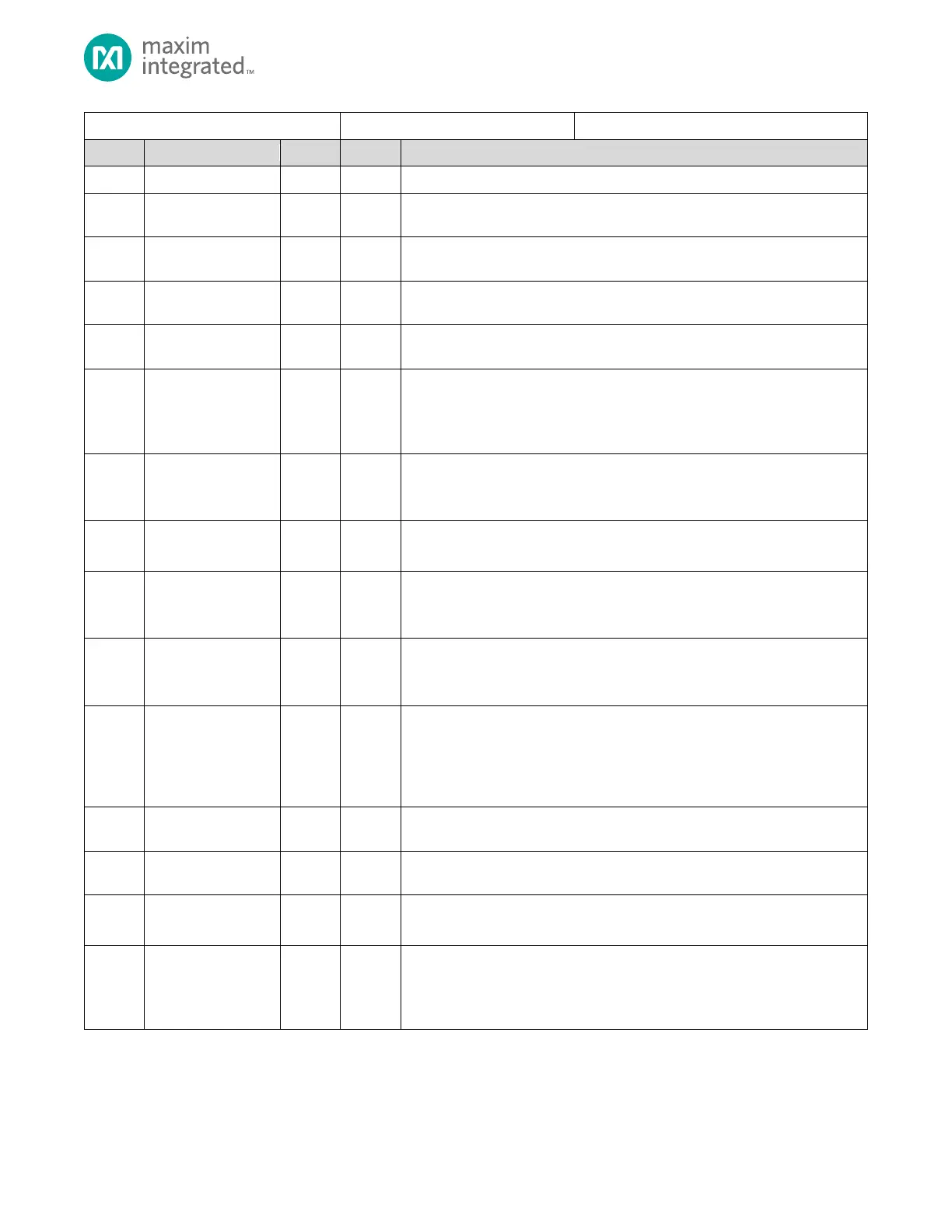

MAX32665-MAX32668 User Guide

Maxim Integrated Page 214 of 457

Voltage Support 1.8V

1: 1.8V supported

Voltage Support 3.0V

1: 3.0V supported

Voltage Support 3.3V

1: 3.3V supported

Suspend/Resume Support

1: Suspend / Resume functionality is supported

SDMA Support

SDMA is supported and can transfer data between system memory and the

SDHC directly.

1: SDMA supported

High Speed Support

The SDHC supports High Speed mode with f

PCLK

=96MHz/2.

1: High speed mode supported

Reserved for Future Use

Do not modify this field.

ADMA2 Support

The SDHC supports ADMA2.

1: ADMA2 supported

8-bit Support for Embedded Device

The SDHC supports 8-bit bus width mode.

0: 8-bit Bus width not supported

Max Block Length

This value indicates the maximum block size that the Host Driver can read and

write to the buffer in the SDHC without wait cycles. The transfer block length is

always 512 bytes for SD memory cards regardless of this field.

0b10: 2048 bytes

Base Clock Frequency for SD Clock

0x00: Get information using another method

Timeout Clock Unit

1: MHz base clock unit

Reserved for Future Use

Do not modify this field.

Timeout Clock Frequency

The base clock frequency used to detect Data Timeout errors. The Timeout

Clock Unit defines the units of this field’s value.

1: 1 [MHz]

Loading...

Loading...