MAX32665-MAX32668 User Guide

Maxim Integrated Page 91 of 457

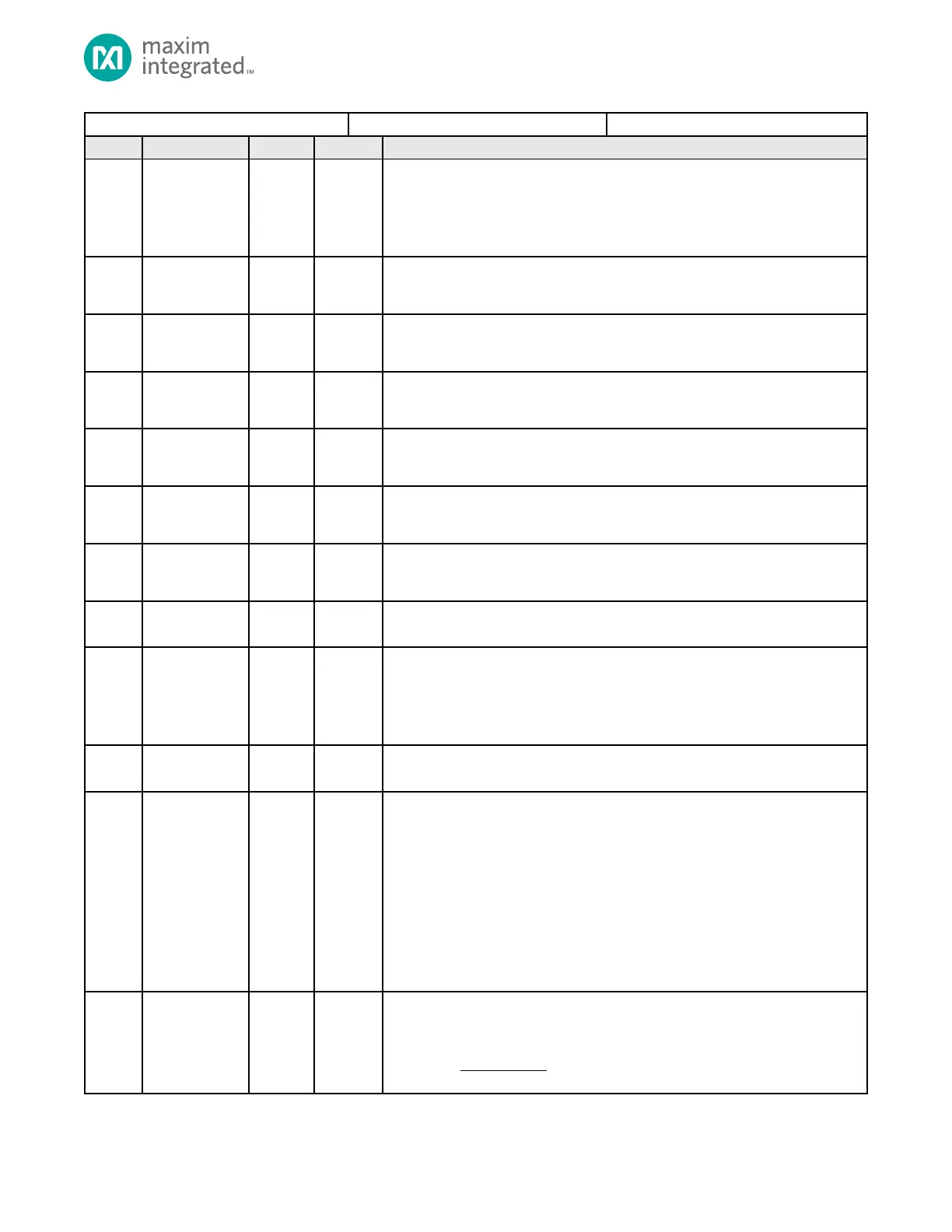

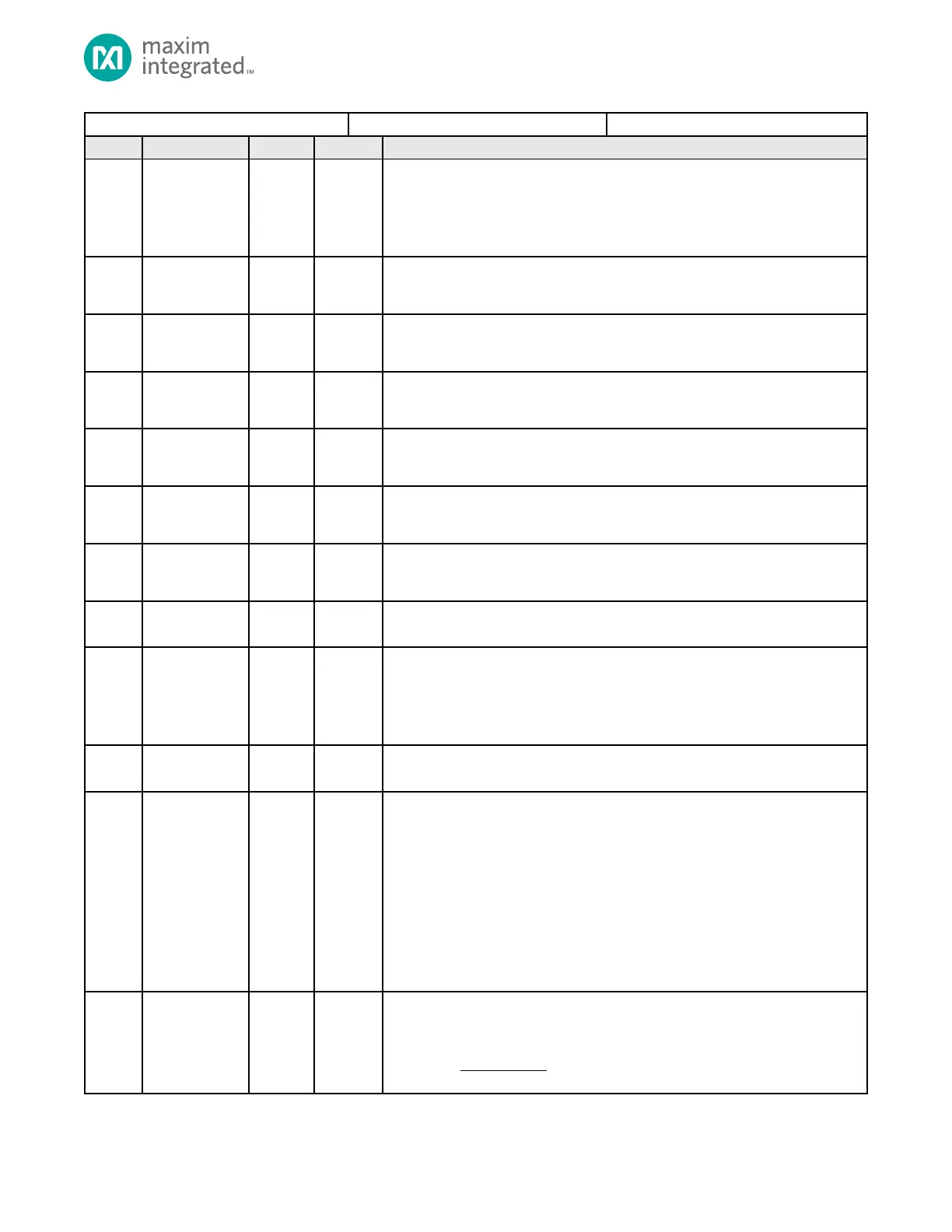

7.3728MHz Internal Oscillator Voltage Source Select

In DEEPSLEEP the 7.3728MHz oscillator voltage is sourced by pin V

DDA

. When

exiting DEEPSLEEP the voltage is automatically switched back to this bit setting.

0: V

COREA

1: Internal 1V regulator sourced from pin V

DDA

7.3728MHz Internal Oscillator Enable

0: Disabled

1: Enabled and ready when GCR_CLK_CTRL.hirc7m_rdy = 1.

96MHz Internal Oscillator Enable

0: Disabled

1: Enabled and ready when GCR_CLK_CTRL.hircmm_rdy = 1.

60MHz Internal Oscillator Enable

0: Disabled

1: Enabled and ready when GCR_CLK_CTRL. hirc60m_rdy = 1.

32.768kHz External Oscillator Enable

0: Disabled

1: Enabled and ready when GCR_CLK_CTRL.x32k_rdy = 1.

32MHz Bluetooth Oscillator Enable

0: Disabled

1: Enabled and ready when GCR_CLK_CTRL.x32m_rdy = 1.

Crypto Accelerator Clock Divider Status

0: Crypto clock divide by 1

1: Crypto clock is divide by 2

Reserved

Do not modify this field.

SYS_OSC Select Ready

When SYS_OSC is changed by modifying sysosc_sel, there is a delay until the

switchover is complete. This bit is cleared until the switchover is complete.

0: Switch to new clock source not yet complete.

1: SYS_OSC is clock source selected in sysosc_sel.

Reserved

Do not modify this field.

System Oscillator Source Select

Selects the system oscillator (SYS_OSC) source used to generate the system clock

(SYS_CLK). Modifying this field immediately clears GCR_CLK_CTRL.sysosc_rdy.

0: 60MHz LP Internal Oscillator

1: Reserved

2: 32MHz Bluetooth Oscillator

3: 8kHz Internal Oscillator

4: 96MHz Internal Oscillator

5: 7.3728MHz Internal Oscillator

6: 32.768kHz External Oscillator

7: Reserved

System Oscillator Prescaler

Sets the divider for generating SYS_CLK from the selected SYS_OSC as shown in the

following equation:

Loading...

Loading...