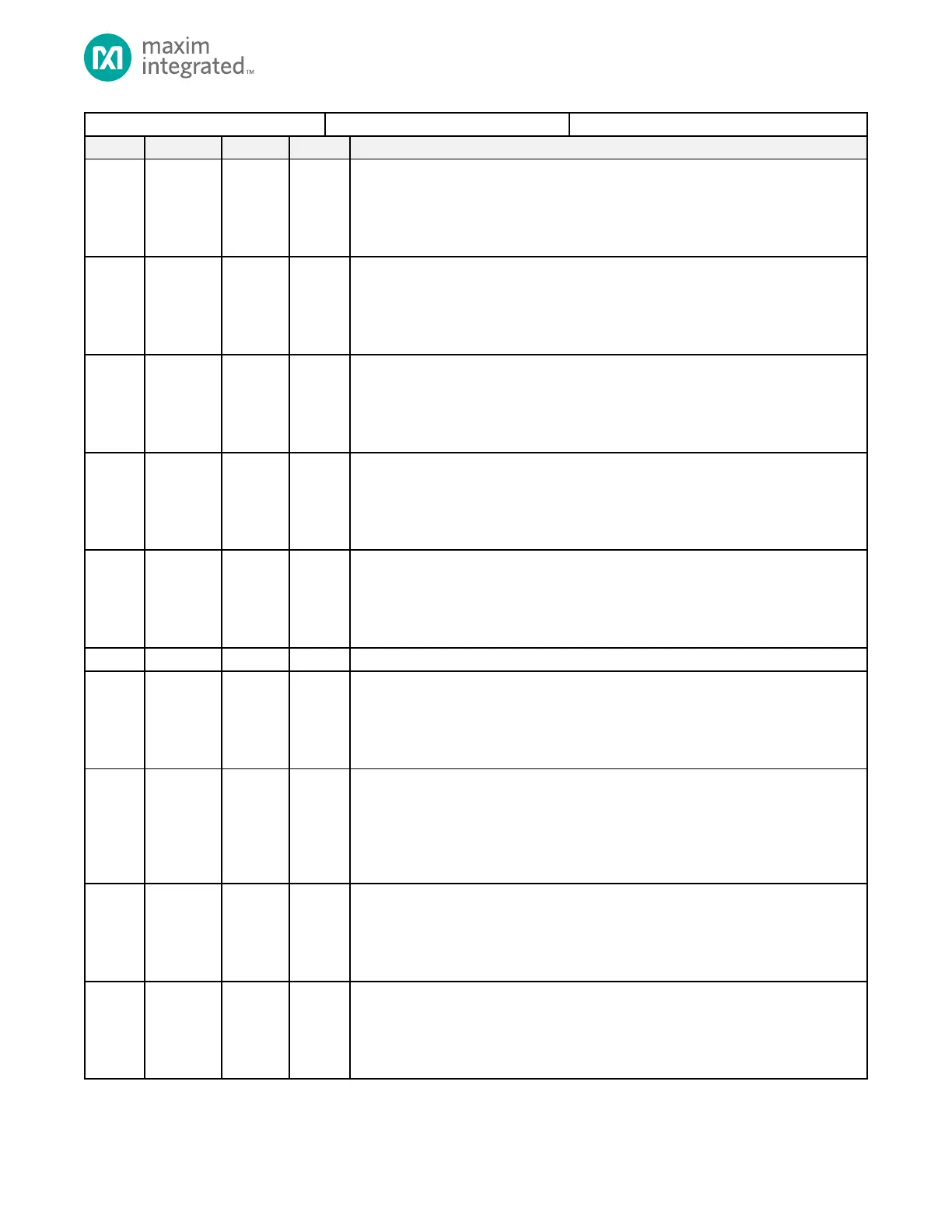

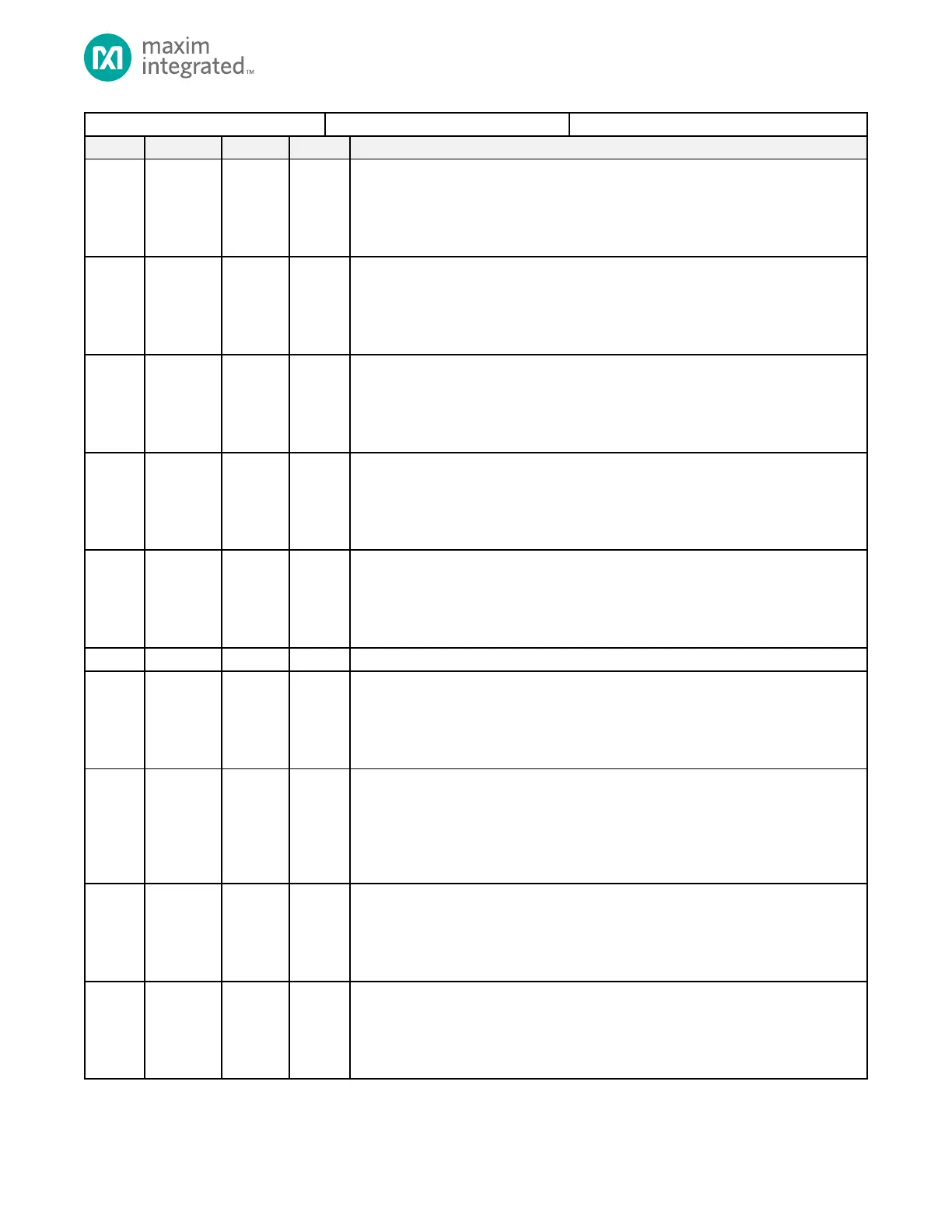

MAX32665-MAX32668 User Guide

Maxim Integrated Page 95 of 457

Peripheral Clocks Disable 0

TMR2 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

TMR1 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

TMR0 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

Crypto Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

I2C0 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

UART1 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

UART0 Clock Disable

Write 1 to disable the clock to the corresponding peripheral. Disabling a clock peripheral

disables functionality while also saving power. Reads and writes to peripheral registers

are disabled. Peripheral register states are retained.

1: Clock disabled to peripheral.

0: Clock enabled to peripheral.

SPI2 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

SPI1 Clock Disable

Disabling a clock disables functionality while also saving power. Reads and writes to

peripheral registers are disabled. Peripheral register states are retained.

0: Clock enabled.

1: Clock disabled.

Loading...

Loading...