43.4.29 USB Clock recovery control (USBx_CLK_RECOVER_CTRL)

Signals in this register control the crystal-less USB clock mode in which the internal

IRC48M oscillator is tuned to match the clock extracted from the incoming USB data

stream.

The IRC48M internal oscillator module must be enabled in register

USB_CLK_RECOVER_IRC_EN for this mode.

Address:

4007_2000h base + 140h offset = 4007_2140h

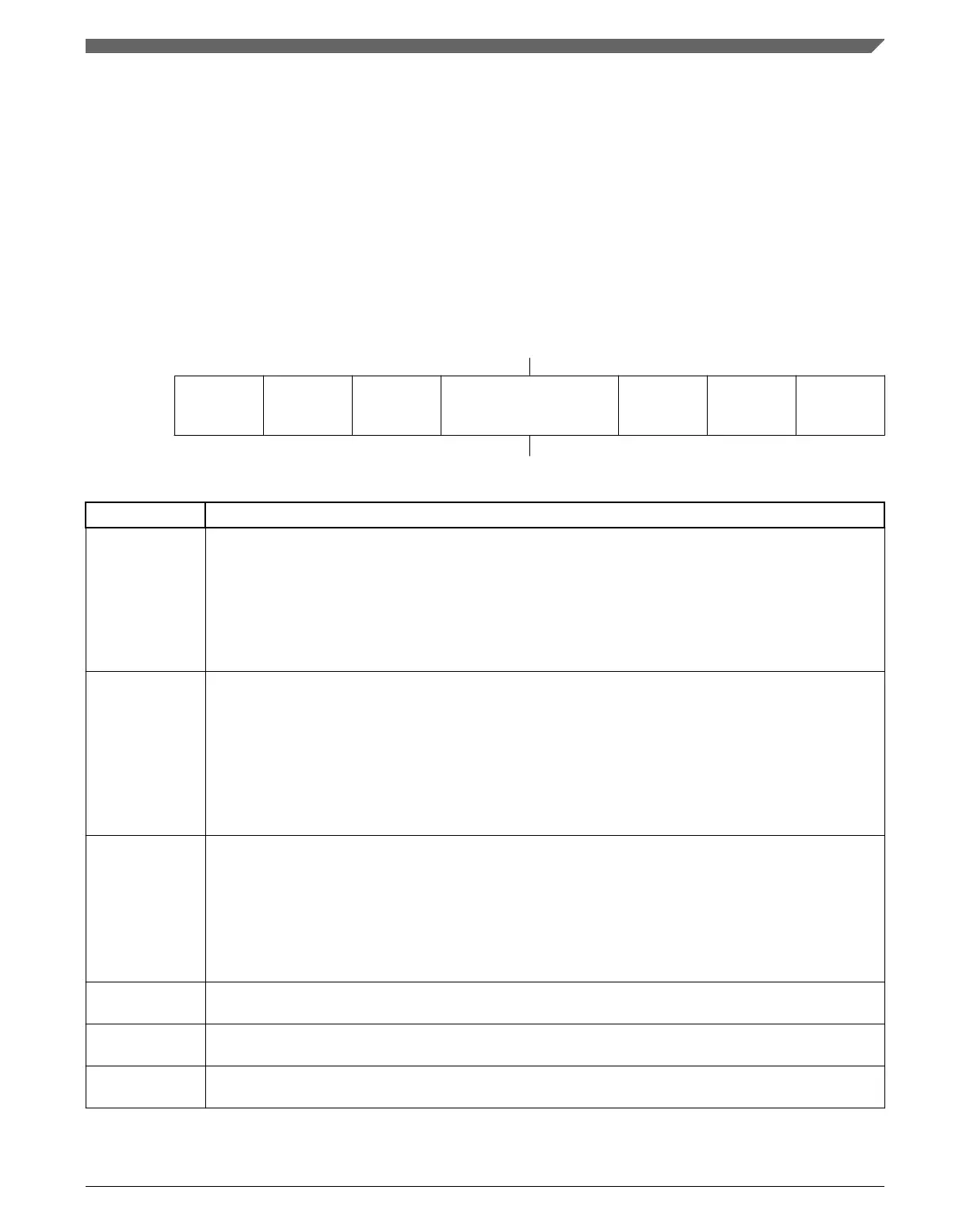

Bit 7 6 5 4 3 2 1 0

Read

CLOCK_

RECOVER_

EN

RESET_

RESUME_

ROUGH_EN

RESTART_

IFRTRIM_

EN

Reserved Reserved Reserved Reserved

Write

Reset

0 0 0 0 0 0 0 0

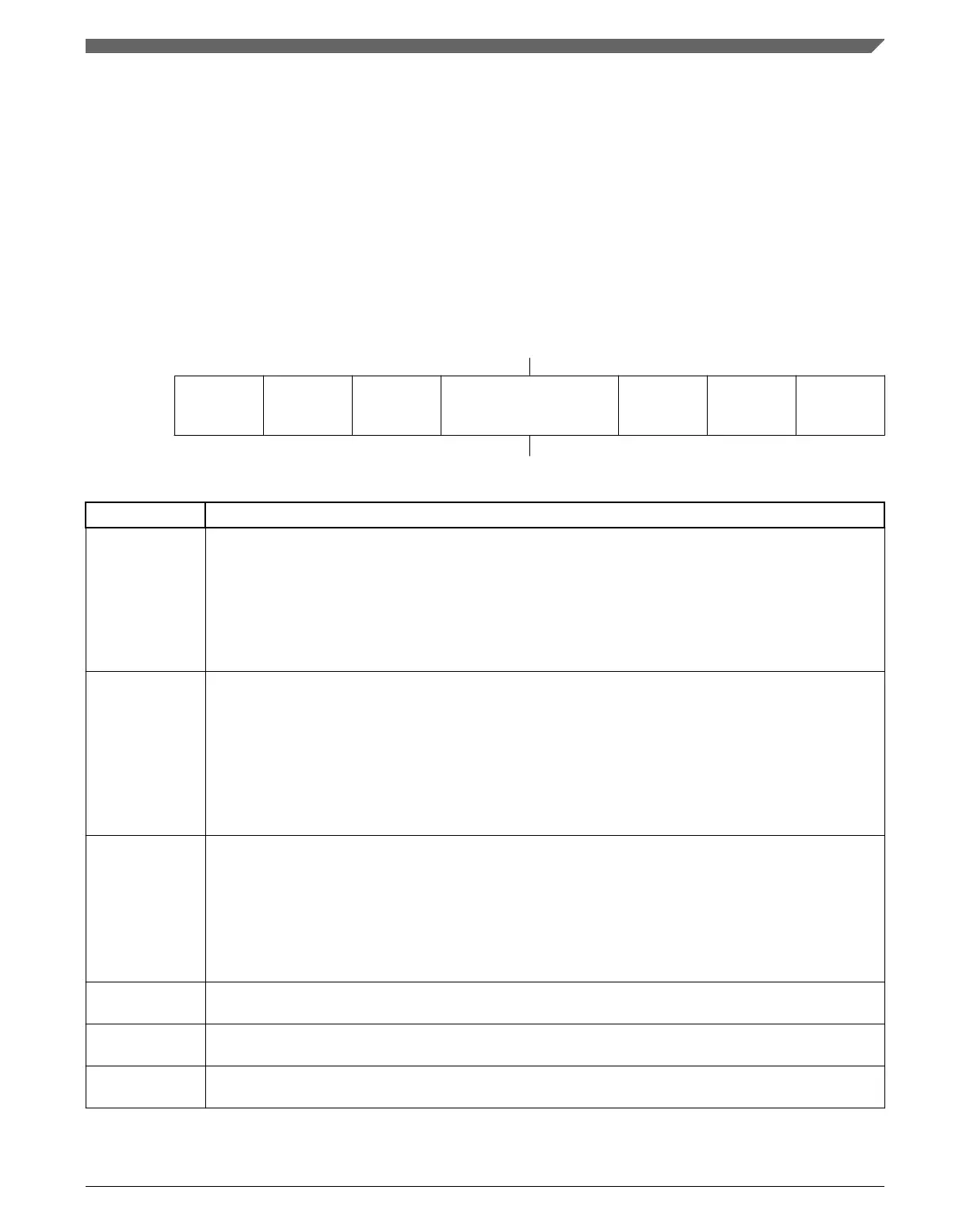

USBx_CLK_RECOVER_CTRL field descriptions

Field Description

7

CLOCK_

RECOVER_EN

Crystal-less USB enable

This bit must be enabled if user wants to use the crystal-less USB mode for the Full Speed USB controller

and transceiver.

NOTE: This bit should not be set for USB host mode or OTG.

0 Disable clock recovery block (default)

1 Enable clock recovery block

6

RESET_

RESUME_

ROUGH_EN

Reset/resume to rough phase enable

The clock recovery block tracks the IRC48Mhz to get an accurate 48Mhz clock. It has two phases after

user enables clock_recover_en bit, rough phase and tracking phase. The step to fine tune the IRC 48Mhz

by adjusting the trim fine value is different during these two phases. The step in rough phase is larger than

that in tracking phase. Switch back to rough stage whenever USB bus reset or bus resume occurs.

0 Always works in tracking phase after the first time rough to track transition (default)

1 Go back to rough stage whenever bus reset or bus resume occurs

5

RESTART_

IFRTRIM_EN

Restart from IFR trim value

IRC48 has a default trim fine value whose default value is factory trimmed (the IFR trim value). Clock

recover block tracks the accuracy of the clock 48Mhz and keeps updating the trim fine value accordingly

0 Trim fine adjustment always works based on the previous updated trim fine value (default)

1 Trim fine restarts from the IFR trim value whenever bus_reset/bus_resume is detected or module

enable is desasserted

4–3

Reserved

This field is reserved.

2

Reserved

This field is reserved.

This bit is for NXP use only. Customers should not change this bit from its default state.

1

Reserved

This field is reserved.

This bit is for NXP use only. Customers should not change this bit from its default state.

Table continues on the next page...

Chapter 43 Universal Serial Bus Full Speed OTG Controller (USBFSOTG)

K22F Sub-Family Reference Manual, Rev. 4, 08/2016

NXP Semiconductors 1107

Loading...

Loading...